# User's Guide

**Digital Signal Processing Products**

1991

## TMS320C4x User's Guide

2564090-9721 revision A May 1991

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1991, Texas Instruments Incorporated

### Preface

## **Read This First**

The purpose of this user's guide is to serve as a reference book for the TMS320C40 and TMS320C40-40 digital signal processors. Throughout the book, all references to the TMS320C40 apply to the TMS320C40-40 as well, unless an exception is noted. This document provides information to assist managers and hardware/software engineers in application development.

#### How to Use This Manual

This document contains the following chapters:

Chapter 1 Introduction

A general description of the TMS320C40, its key features, and typical applications.

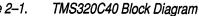

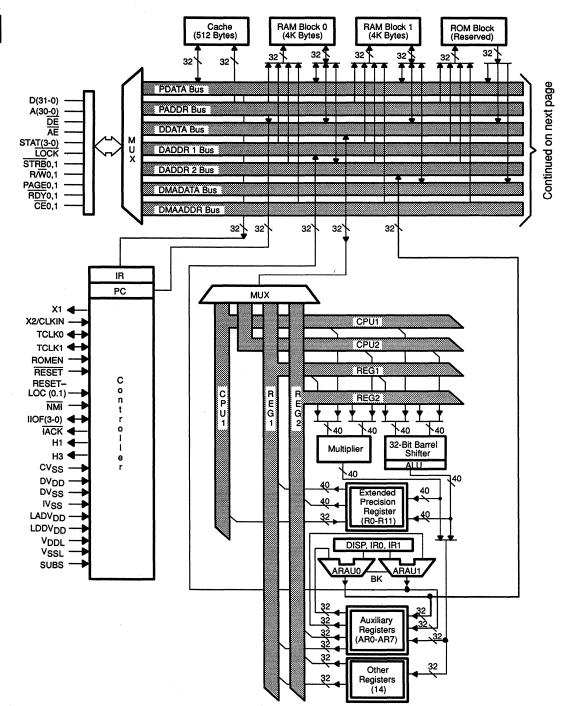

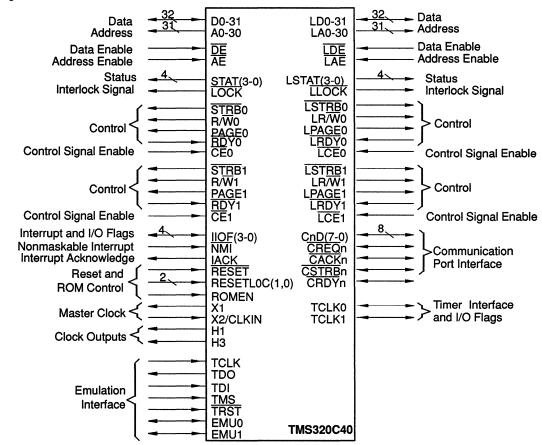

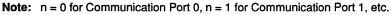

Chapter 2 Architectural Overview Functional block diagrams. TMS320C40 design description, hardware components, and device operation. Instruction set summary.

Chapter 3 CPU Registers, Memory, and Cache Description of the registers in the CPU primary register file and expansion register file. Memory maps. Instruction cache architecture, algorithm, and control bits.

#### Chapter 4 Data Formats and Floating-Point Operation Description of signed and unsigned integer and floating-point formats. Discussion of floating-point multiplication, addition, subtraction, normalization, rounding, conversions, and reciprocals.

#### Chapter 5 Addressing

Addressing types. Operation, encoding, and implementation of addressing modes. Format descriptions. Circular and bit-reversed addressing. System stack management.

#### Chapter 6 Program Flow Control

Software control of program flow using repeat modes, different types of branching, traps, interrupts, and interlocked operations. Reset operation, including resulting values in registers and on pins.

#### Chapter 7 External Bus Operation

Discussion of the two 80-pin local and global memory interfaces. Programmable wait-states. Memory access timing. Signal group control. Interlocked instructions. Interrupt acknowledge timing.

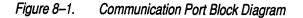

#### Chapter 8 Communication Ports

Description of the six, bidirectional, 160-megabit-per-second (at 40-ns cycle time) communication ports designed for sharing tasks between processors. Memory maps of the ports and their registers. Port operation and coordination of port activity with CPU and DMA coprocessors.

#### Chapter 9 DMA Coprocessors and 'C40 Timers

DMA coprocessor operation. Description of coprocessor registers (channel control, channel address, index, transfer count, and link pointer). Use in unified and split mode. Priority and CPU/DMA arbitration. Autoinitialization and interrupts. Operation of the 'C40 timers; their registers (global control, timer counter, and period).

#### Chapter 10 Pipeline Operation

Discussion of 'C40 pipeline operations. This includes pipeline conflicts and methods for resolving these. Clocking of memory accesses.

#### Chapter 11 Assembly Language Instructions

Functional listing of instructions. Condition code definitions (for conditional instructions such as branch conditional). Alphabetized individual instruction descriptions with examples.

#### Chapter 12 Software Applications

Software application examples for using various TMS320C40 instruction-set and programming features. Code listings enhance explanations.

#### **Chapter 13 Hardware Applications**

Hardware design techniques and application examples for interfacing to memories, peripherals, or other microcomputers/microprocessors. Code listings, schematics, and timing diagrams facilitate explanations.

#### Chapter 14 TMS320C4x Signal Descriptions and Electrical Characteristics

Pin locations and pin descriptions. 'C40 dimensions and package description. Electrical characteristics. Signal timing and characteristics.

#### Appendix A TMS320C40 Sockets

Two sockets available for the TMS320C40.

#### Appendix B XDS510 Design Considerations

Considerations for designing your TMS320C40 target system for use with the XDS510 emulator.

#### References

The publications in the following reference list contain useful information regarding functions, operations, and applications of digital signal processing. These books also provide other references to many useful technical papers. The reference list is organized into categories of general DSP, speech, image processing, and digital control theory, and is alphabetized by author.

#### **General Digital Signal Processing:**

Antoniou, Andreas, *Digital Filters: Analysis and Design*. New York, NY: McGraw-Hill Company, Inc., 1979.

Brigham, E. Oran, *The Fast Fourier Transform*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1974.

Burrus, C.S., and Parks, T.W., *DFT/FFT and Convolution Algorithms*. New York, NY: John Wiley and Sons, Inc., 1984.

*Digital Signal Processing Applications with the TMS320 Family.* Texas Instruments, 1986; Prentice-Hall, Inc., 1987.

Gold, Bernard, and Rader, C.M., *Digital Processing of Signals*. New York, NY: McGraw-Hill Company, Inc., 1969.

Hamming, R.W., *Digital Filters*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

IEEE ASSP DSP Committee (Editor), *Programs for Digital Signal Processing*. New York, NY: IEEE Press, 1979.

Jackson, Leland B., *Digital Filters and Signal Processing*. Hingham, MA: Kluwer Academic Publishers, 1986.

Jones, D.L., and Parks, T.W., *A Digital Signal Processing Laboratory Using the TMS32010*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

Lim, Jae, and Oppenheim, Alan V. (Editors), *Advanced Topics in Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1988.

Morris, L. Robert, *Digital Signal Processing Software*. Ottawa, Canada: Carleton University, 1983.

Meyer, Riamund and Schwartz, Karl, FFT Implementation on DSP Chips — Theory and Practice, Proceedings of ICAASP 90, vol. 3, 1990

Oppenheim, Alan V. (Editor), *Applications of Digital Signal Process-ing.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

Oppenheim, Alan V., and Schafer, R.W., *Digital Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

Oppenheim, Alan V., and Willsky, A.N., with Young, I.T., *Signals and Systems*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

Parks, T.W., and Burrus, C.S., *Digital Filter Design*. New York, NY: John Wiley and Sons, Inc., 1987.

Rabiner, Lawrence R., and Gold, Bernard, *Theory and Application of Digital Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

Sorensen, Henrik V., Jones, Douglas, Heideman, M.T., and Burris, C.S., *Real-Valued Fast Fourier Transform Algorithms,* IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. ASSP–35, no. 6, June 1987.

Treichler, J.R., Johnson, Jr., C.R., and Larimore, M.G., *Theory and Design of Adaptive Filters*. New York, NY: John Wiley and Sons, Inc., 1987.

#### **G** Speech:

Gray, A.H., and Markel, J.D., *Linear Prediction of Speech*. New York, NY: Springer-Verlag, 1976.

Jayant, N.S., and Noll, Peter, *Digital Coding of Waveforms*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

Papamichalis, Panos, *Practical Approaches to Speech Coding*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

Rabiner, Lawrence R., and Schafer, R.W., *Digital Processing of Speech Signals*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

#### Image Processing:

Andrews, H.C., and Hunt, B.R., *Digital Image Restoration*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

Gonzales, Rafael C., and Wintz, Paul, *Digital Image Processing*. Reading, MA: Addison-Wesley Publishing Company, Inc., 1977.

Pratt, William K., *Digital Image Processing*. New York, NY: John Wiley and Sons, 1978.

#### **Digital Control Theory:**

Jacquot, R., *Modern Digital Control Systems*. New York, NY: Marcel Dekker, Inc., 1981.

Katz, P., *Digital Control Using Microprocessors*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1981.

Kuo, B.C., *Digital Control Systems*. New York, NY: Holt, Reinholt and Winston, Inc., 1980.

Moroney, P., *Issues in the Implementation of Digital Feedback Compensators.* Cambridge, MA: The MIT Press, 1983.

Phillips, C., and Nagle, H., *Digital Control System Analysis and De*sign. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

#### Style and Symbol Conventions

This document uses the following conventions:

Program listings, program examples, interactive displays, file names, and symbol names are shown in a special font. Examples use a bold version of the special font for emphasis. Here is a sample program listing:

| 0011 | 0005 | 0001 | .field | 1, | 2 |

|------|------|------|--------|----|---|

| 0012 | 0005 | 0003 | .field | з, | 4 |

| 0013 | 0005 | 0006 | .field | 6, | 3 |

| 0014 | 0006 |      | .even  |    |   |

In syntax descriptions, the instruction, command, or directive is in a **bold face font** and parameters are in *italics*. Portions of a syntax that are in **bold face** should be entered as shown; portions of a syntax that are in *italics* describe the *type* of information that should be entered. Here is an example of an instruction:

#### CMPF3 src2, src3

Note: Although the instruction mnemonic (CMPF3 in this example) is in capital letters, the 'C40 assembler **is not case sensitive** — it can assemble mnemonics entered in either upper or lower case.

**CMPF3** is the instruction mnemonic. This instruction has two parameters, indicated by *src2* and *src3*.

Square brackets ([and]) identify an optional parameter. If you use an optional parameter, you must specify the information within the brackets; however, you don't enter the brackets themselves. Here's an example of an instruction that has an optional parameter:

#### LDP src [,DP]

The **LDP** instruction is shown with two parameters; one is optional. The first parameter, *src*, is required. The second parameter, *DP*, is optional. As this syntax shows, if you use the optional second parameter, you must precede it with a comma.

Braces ( { and } ) indicate a list. The symbol | (read as or) separates items within the list. Here's an example of a list:

{ \* | \*+ | \*- }

This provides three choices: \*, \*+, or \*-.

Unless the list is enclosed in square brackets, you must choose one item from the list.

The following is the format for a varying number of parameters. For example, the .byte directive can have up to 100 parameters. The syntax for this directive is

**.byte** value<sub>1</sub> [, ... , value<sub>n</sub>]

This syntax shows that .byte must have at least one value parameter, but you have the option of supplying additional value parameters separated by commas.

#### Information About Cautions and Warnings

A caution describes a situation that could potentially damage your software or equipment.

A warning describes a situation that could potentially cause harm to you.

Please read each caution or warning carefully. The information is provided for your protection.

#### Trademarks

ABEL is a trademark of the Data I/O Corporation.

SPOX is a trademark of Spectron Microsystems, Inc.

## Contents

| 1 | Intro | duction  |                                                                 |

|---|-------|----------|-----------------------------------------------------------------|

|   | 1.1   | The T    | MS320 Family                                                    |

|   | 1.2   |          | el Processing                                                   |

|   | 1.3   |          | 20C4x Features                                                  |

|   |       | 1.3.1    | TMS320C40 Device Key Features 1-4                               |

|   |       | 1.3.2    | Communication Port Benefits 1-7                                 |

|   |       | 1.3.3    | DMA Coprocessor Benefits 1-8                                    |

|   |       | 1.3.4    | TMS320C40 Parallel Processing Development Tools<br>Key Features |

|   | 1.4   | Applica  | ations 1-11                                                     |

| 2 | Archi | itectura | l Overview                                                      |

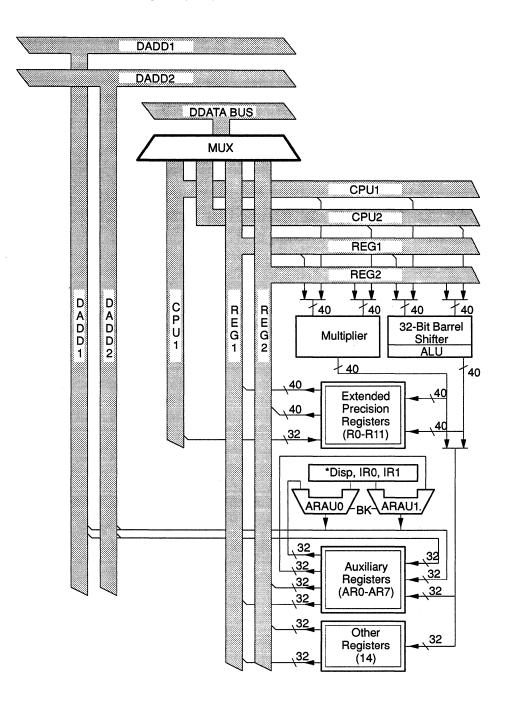

|   | 2.1   | Centra   | Il Processing Unit (CPU)                                        |

|   |       | 2.1.1    | Multiplier 2-4                                                  |

|   |       | 2.1.2    | Arithmetic Logic Unit (ALU) 2-4                                 |

|   |       | 2.1.3    | Auxiliary Register Arithmetic Units (ARAUs) 2-6                 |

|   |       | 2.1.4    | CPU Primary Register File 2-6                                   |

|   |       | 2.1.5    | CPU Expansion Register File 2-9                                 |

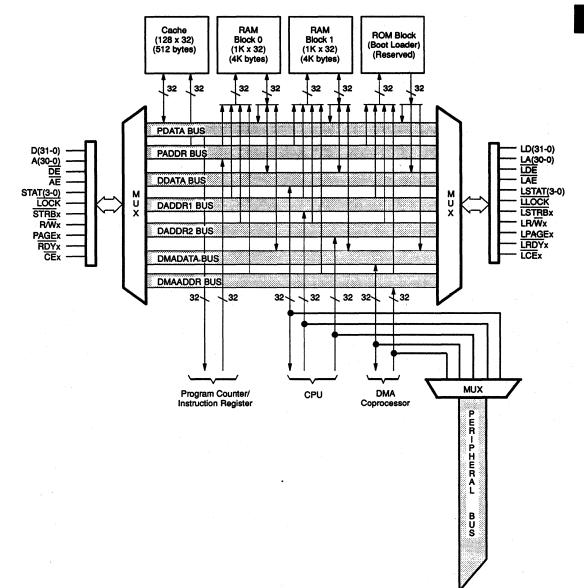

|   | 2.2   | Memo     | ry Organization 2-10                                            |

|   |       | 2.2.1    | RAM, ROM, and Cache 2-10                                        |

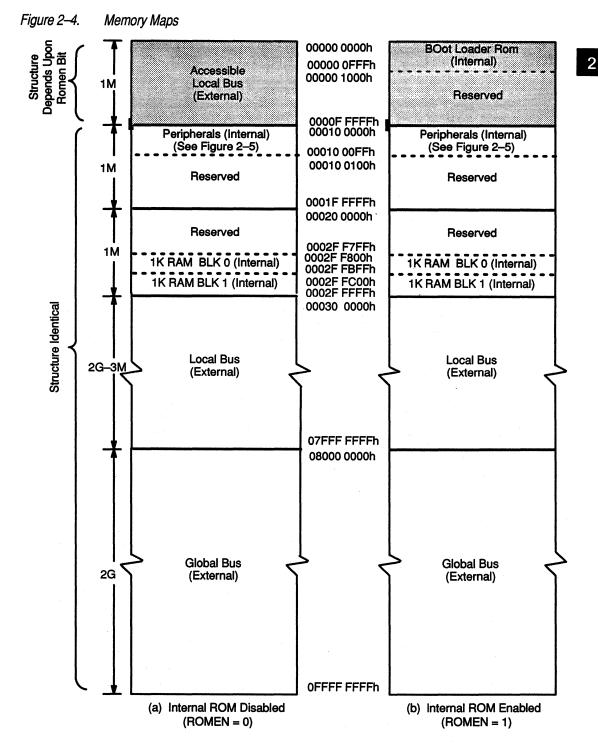

|   |       | 2.2.2    | Memory Maps                                                     |

|   |       | 2.2.3    | Memory Addressing Modes 2-15                                    |

|   | 2.3   | Instruc  | tion Set Summary                                                |

|   | 2.4   |          | al Bus Operation                                                |

|   | 2.5   |          | al Bus Operation                                                |

|   |       | 2.5.1    | Interrupts                                                      |

|   |       | 2.5.2    | Interlocked Instructions                                        |

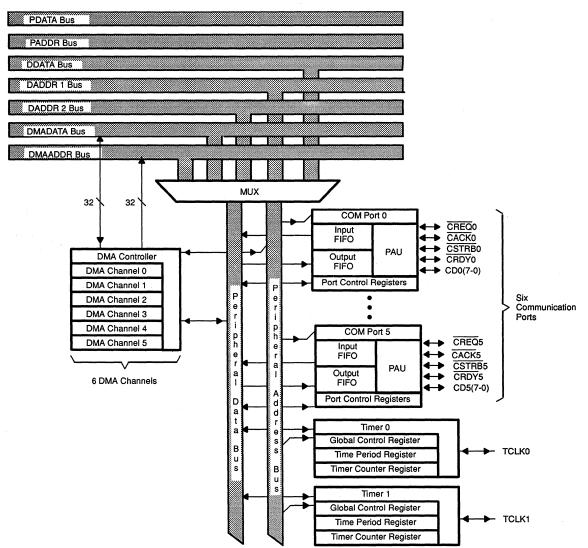

|   | 2.6   | Periph   | erals                                                           |

|   |       | 2.6.1    | Communication Ports 2-29                                        |

|   |       | 2.6.2    | Direct Memory Access (DMA) 2-29                                 |

|   |       | 2.6.3    | Timers                                                          |

| 3 | CPU   | Registe  | ers, Memory, and Cache                                          |

|   | 3.1   |          | Primary Register File                                           |

|   |      | 3.1.1    | Extended-Precision Registers (R0–R11)                                           | 3-4    |

|---|------|----------|---------------------------------------------------------------------------------|--------|

|   |      | 3.1.2    | Auxiliary Registers (AR0–AR7)                                                   | 3-5    |

|   |      | 3.1.3    | Data-Page Pointer (DP)                                                          | 3-5    |

|   |      | 3.1.4    | Index Registers (IR0, IR1)                                                      | 3-5    |

|   |      | 3.1.5    | Block-Size Register (BK)                                                        | 3-5    |

|   |      | 3.1.6    | System Stack Pointer (SP)                                                       | 3-5    |

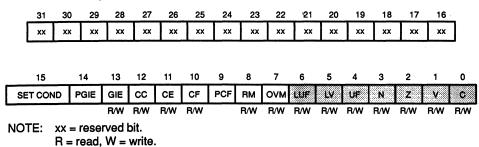

|   |      | 3.1.7    | Status Register (ST)                                                            | 3-5    |

|   |      | 3.1.8    | DMA Coprocessor Interrupt Enable Register (DIE)                                 | 3-8    |

|   |      | 3.1.9    | CPU Internal Interrupt Enable Register (IIE)                                    | . 3-10 |

|   |      | 3.1.10   | IIOF Flag Register (IIF) Controls External Pins IIOF(3 – 0),<br>Timer/DMA Flags | . 3-12 |

|   |      | 3.1.11   | Block-Repeat (RS, RE) and Repeat-Count (RC) Registers                           | . 3-14 |

|   |      | 3.1.12   | Program Counter (PC)                                                            | . 3-14 |

|   |      | 3.1.13   | Reserved Bits and Compatibility                                                 | . 3-14 |

|   | 3.2  | CPU E    | xpansion Register File                                                          |        |

|   | 3.3  | RESET    | Vector Mapping                                                                  | . 3-17 |

|   | 3.4  | Memor    | у                                                                               | . 3-18 |

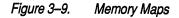

|   |      | 3.4.1    | Overall Memory Map                                                              | . 3-19 |

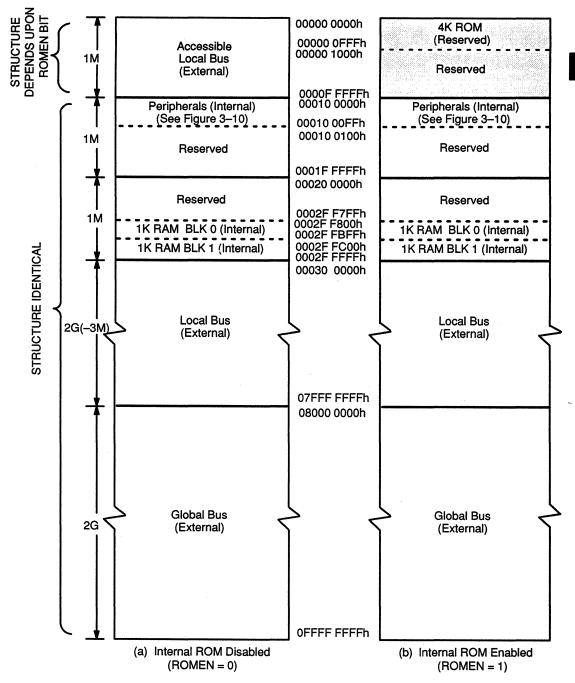

|   |      | 3.4.2    | Peripheral Bus Memory Map                                                       | . 3-20 |

|   | 3.5  | Instruct | tion Cache Architecture                                                         | . 3-25 |

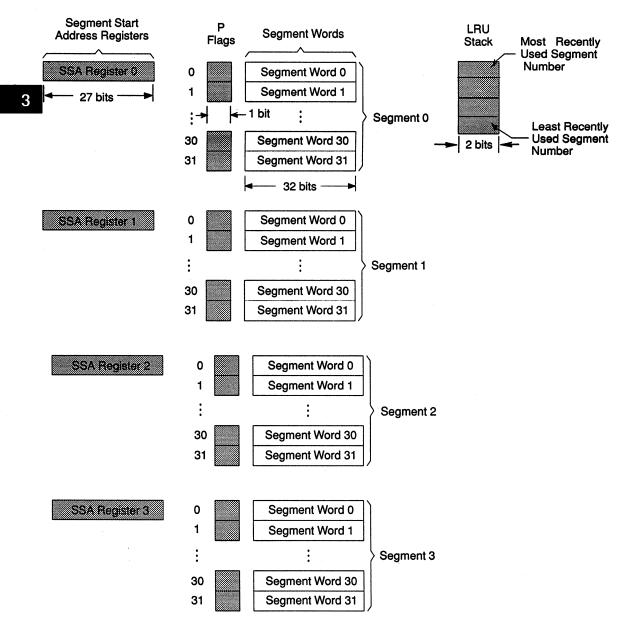

|   |      | 3.5.1    | Cache Algorithm                                                                 | . 3-27 |

|   |      | 3.5.2    | Cache and System Memory                                                         | . 3-28 |

|   |      | 3.5.3    | Cache Control Bits                                                              | . 3-29 |

| 4 | Data | Formate  | s and Floating-Point Operation                                                  | 4-1    |

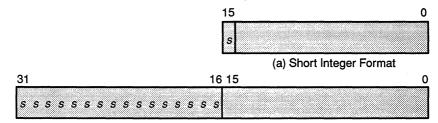

|   | 4.1  | Signed   | Integer Formats                                                                 | 4-3    |

|   |      | 4.1.1    | Short Integer Format                                                            |        |

|   |      | 4.1.2    | Single-Precision Integer Format                                                 | 4-3    |

|   | 4.2  | Unsign   | ed-Integer Formats                                                              | 4-4    |

|   |      | 4.2.1    | Short Unsigned-Integer Format                                                   | 4-4    |

|   |      | 4.2.2    | Single-Precision Unsigned-Integer Format                                        | 4-4    |

|   | 4.3  | Floatin  | g-Point Formats                                                                 |        |

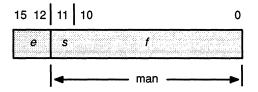

|   |      | 4.3.1    | Short Floating-Point Format                                                     | 4-6    |

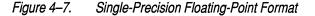

|   |      | 4.3.2    | Single-Precision Floating-Point Format                                          |        |

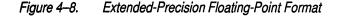

|   |      | 4.3.3    | Extended-Precision Floating-Point Format                                        | 4-8    |

|   |      | 4.3.4    | Conversion Between Floating-Point Formats                                       | 4-9    |

|   | 4.4  | Floatin  | g-Point Conversions (IEEE Std. 754/'C4x)                                        | . 4-11 |

|   |      | 4.4.1    | Converting IEEE Format to Twos-Complement<br>Floating-Point Format              |        |

|   |      | 4.4.2    | Converting Twos-Complement Floating-Point Format to IEEE Format                 | . 4-13 |

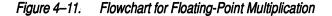

|   | 4.5   | Floating | g-Point Multiplication                            | 4-15  |

|---|-------|----------|---------------------------------------------------|-------|

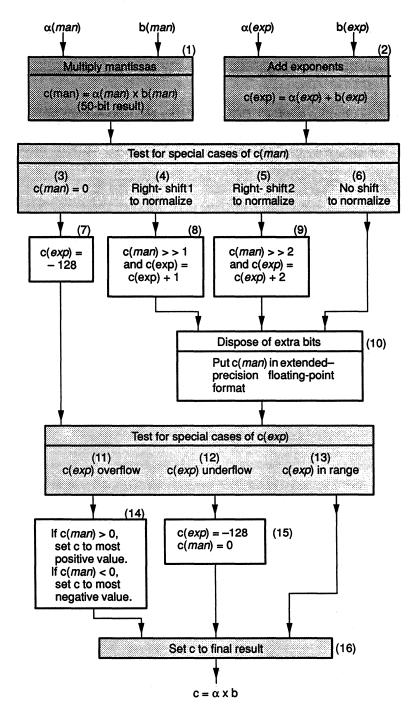

|   | 4.6   | Floating | g-Point Addition and Subtraction                  | 4-20  |

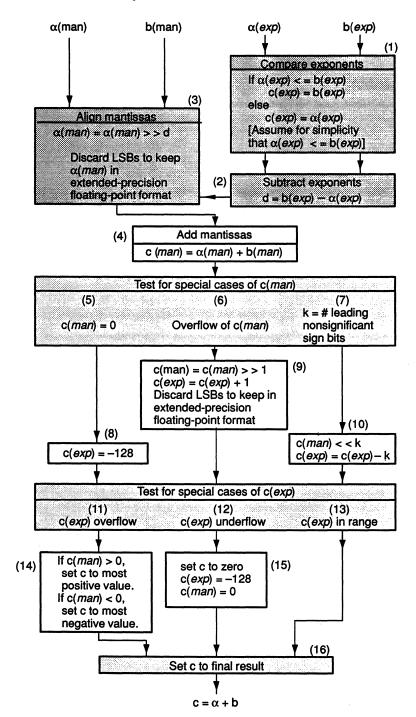

|   | 4.7   | Normal   | ization (NORM Instruction)                        | 4-24  |

|   | 4.8   |          | ng (RND Instruction)                              |       |

|   | 4.9   |          | g-Point-to-Integer Conversion (FIX Instruction)   |       |

|   | 4.10  |          | -to-Floating-Point Conversion (FLOAT Instruction) |       |

|   | 4.11  | Recipro  | ocal (RCPF Instruction)                           |       |

|   |       | 4.11.1   | ····F·································            |       |

|   | 4.12  | Recipro  | cal Square Root (RSQRF Instruction)               | 4-33  |

|   |       |          | Reciprocal Square Root Algorithm                  |       |

|   |       | 4.12.2   | Background on the Reciprocal Square Root          | 4-35  |

| 5 | Addre | essing . |                                                   | . 5-1 |

|   | 5.1   | Types of | of Addressing                                     | . 5-2 |

|   |       | 5.1.1    | Register Addressing                               | . 5-3 |

|   |       | 5.1.2    | Direct Addressing                                 | . 5-4 |

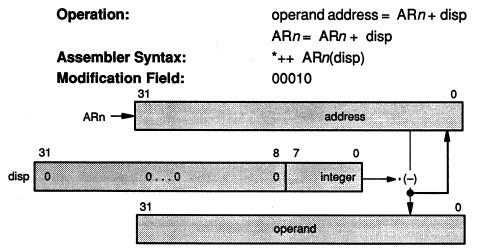

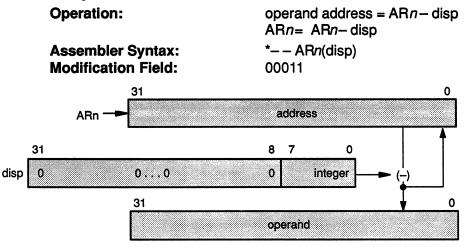

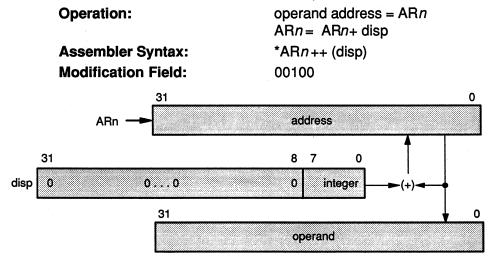

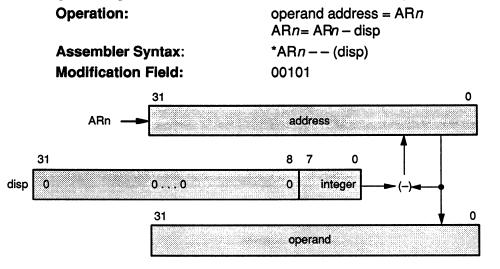

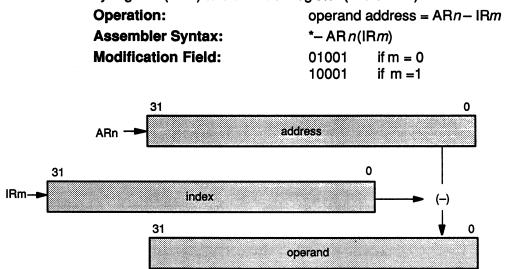

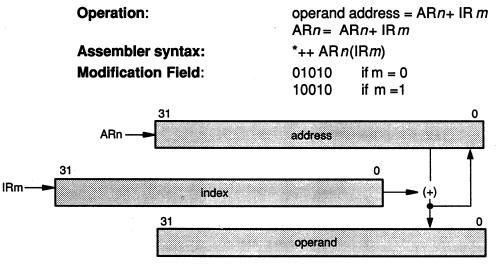

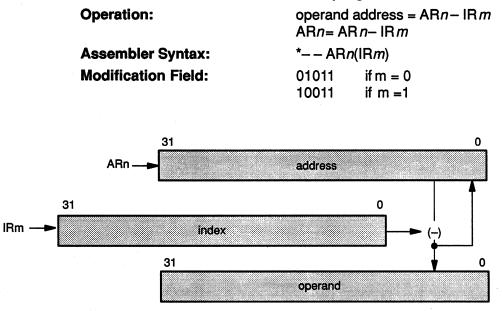

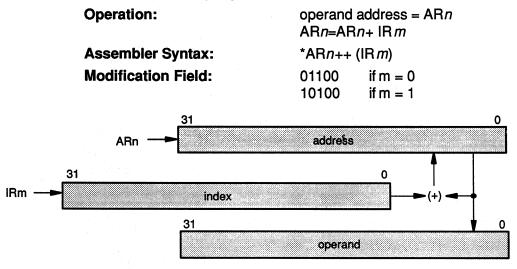

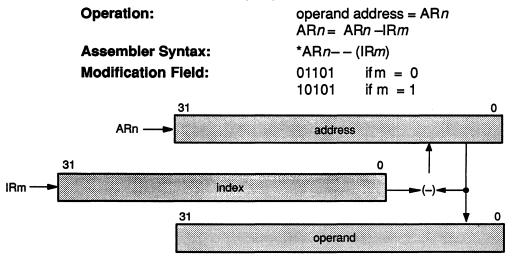

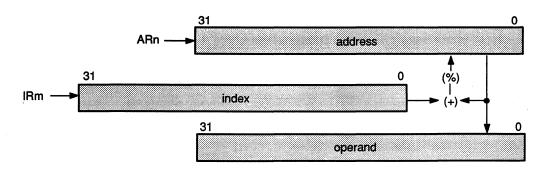

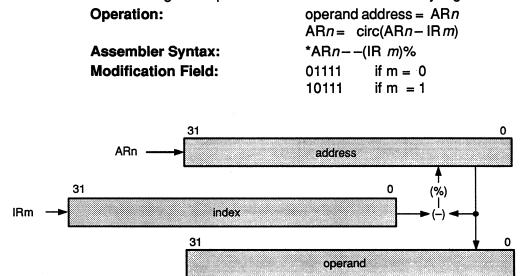

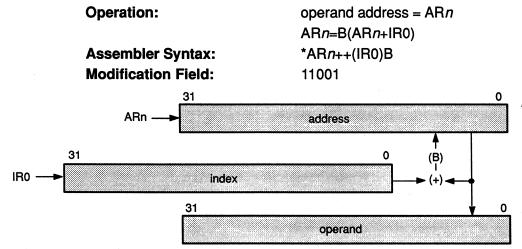

|   |       | 5.1.3    | Indirect Addressing                               | . 5-5 |

|   |       | 5.1.4    | Immediate Addressing                              | 5-17  |

|   |       | 5.1.5    | PC-Relative Addressing                            | 5-17  |

|   | 5.2   | Groups   | s of Addressing Modes                             | 5-19  |

|   |       | 5.2.1    | General Addressing Modes                          | 5-19  |

|   |       | 5.2.2    | Three-Operand Addressing Modes                    | 5-20  |

|   |       | 5.2.3    | Parallel Addressing Modes                         | 5-23  |

|   |       | 5.2.4    | Conditional-Branch Addressing Modes               | 5-24  |

|   | 5.3   | Circula  | r Addressing                                      | 5-25  |

|   | 5.4   | Bit-Rev  | versed Addressing                                 | 5-30  |

|   | 5.5   | System   | and User Stack Management                         | 5-31  |

|   |       | 5.5.1    | Stacks                                            | 5-32  |

|   |       | 5.5.2    | Queues and Dequeues                               | 5-33  |

| 6 | Progr | am Flov  | w Control                                         | . 6-1 |

|   | 6.1   | Repeat   | : Modes                                           | . 6-2 |

|   |       | 6.1.1    |                                                   |       |

|   |       | 6.1.2    | RPTB and RPTBD Initialization                     | . 6-3 |

|   |       | 6.1.3    | RPTS Initialization                               | . 6-4 |

|   |       | 6.1.4    | Repeat-Mode Operation                             | . 6-4 |

|   | 6.2   | Delaye   | d Branches                                        | . 6-7 |

|   | 6.3   | Calls, T | raps, Branches, Jumps, and Returns                | . 6-9 |

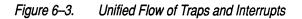

|   | 6.4   | Unifying | g Traps and Interrupts                            | 6-11  |

|   |       | 6.4.1    | Initialization                                    | 6-11  |

|   |       | 6.4.2    | Operation                                         | 6-11  |

|   | 6.5<br>6.6<br>6.7 | Reset C<br>Interrup<br>6.7.1 | ked Operations       6-13         operation       6-18         ts       6-23         Interrupt Control Bits       6-24         Prioritization and Control       6-24 |

|---|-------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 |                   |                              | Operation                                                                                                                                                            |

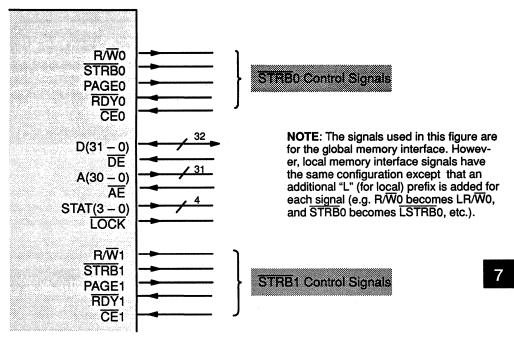

|   | 7.1               | •                            | and Local) Memory Interface Control Signals                                                                                                                          |

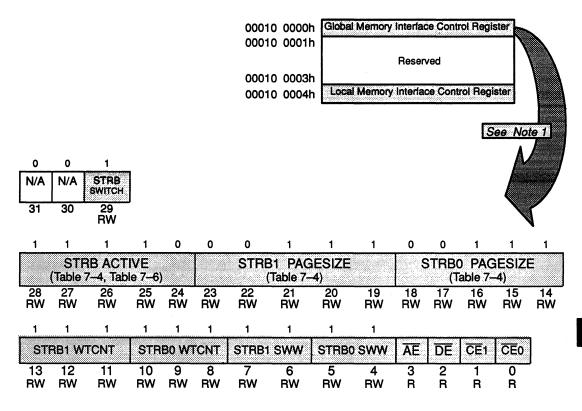

|   | 7.2               | •                            | Interface Control Registers                                                                                                                                          |

|   | 7.3               |                              | he Global Memory Interface Registers                                                                                                                                 |

|   |                   |                              | Mapping Addresses to Strobes                                                                                                                                         |

|   | -                 |                              | Page Size Operation                                                                                                                                                  |

|   | 7.4               | -                            | nmable Wait States                                                                                                                                                   |

|   | 7.5               |                              | 7-17                                                                                                                                                                 |

|   | 7.6<br>7.7        |                              | nabled Signals to Control Signal Group                                                                                                                               |

|   | 7.7<br>7.8        |                              | ked-Instructions Definition and Bus Timing       7-39         ming       7-47                                                                                        |

|   | 7.0               | IACK II                      | ming                                                                                                                                                                 |

| 8 | Comn              | nunicati                     | on Ports                                                                                                                                                             |

|   | 8.1               | Introduc                     | stion                                                                                                                                                                |

|   | 8.2               | Commu                        | nication Port Features                                                                                                                                               |

|   | 8.3               | Operatio                     | onal Overview                                                                                                                                                        |

|   | 8.4               | Commu                        | nication Port Memory Map and Registers                                                                                                                               |

|   |                   | 8.4.1                        | Communication Port Control Registers (CPCRs) 8-9                                                                                                                     |

|   |                   | 8.4.2                        | Input Port Register                                                                                                                                                  |

|   |                   | 8.4.3                        | Output Port Register 8-9                                                                                                                                             |

|   | 8.5               | Commu                        | nication Port Operation                                                                                                                                              |

|   |                   | 8.5.1                        | Port Arbitration Units (PAUs)                                                                                                                                        |

|   |                   | 8.5.2                        | Module Reset                                                                                                                                                         |

|   |                   | 8.5.3                        | Halting of Input and Output FIFOs 8-15                                                                                                                               |

|   | 8.6               | Coordin                      | ating Communication Port Activity With CPU and DMA                                                                                                                   |

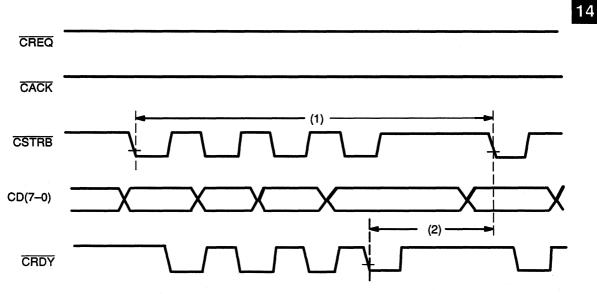

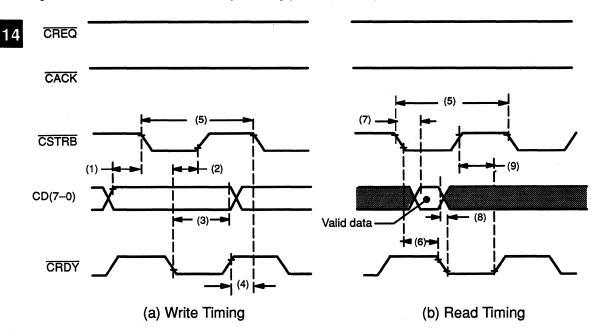

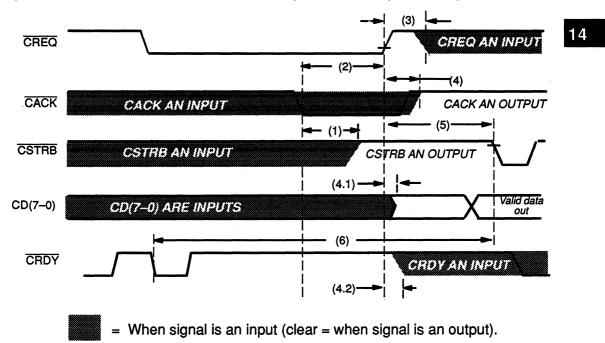

|   | 8.7               | •                            | nication Port Timing                                                                                                                                                 |

|   | 0.7               |                              | Timing Table and Figures                                                                                                                                             |

|   |                   |                              | Synchronizer Timing                                                                                                                                                  |

| • | <b>B</b> 144      |                              |                                                                                                                                                                      |

| 9 |                   | -                            | essor and 'C40 Timers                                                                                                                                                |

|   | 9.1               |                              | 22 stion                                                                                                                                                             |

|   | 9.2               |                              | oprocessor Functional Description                                                                                                                                    |

|   | 9.3               |                              | oprocessor Registers                                                                                                                                                 |

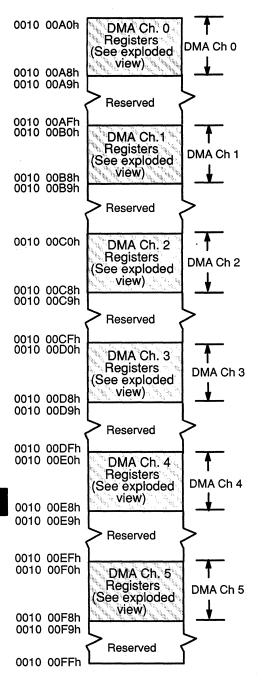

|   |                   | 9.3.1                        | DMA Channel Control Register                                                                                                                                         |

|   |                   | 9.3.2                        | DMA Channel Address and Index Registers                                                                                                                              |

|    |        | 9.3.3   | DMA Channel Transfer-Counter and Auxiliary-Transfer-Count Registers | 9-18   |

|----|--------|---------|---------------------------------------------------------------------|--------|

|    |        | 9.3.4   | DMA-Channel Link-Pointer and Auxiliary-Link-Pointer<br>Registers    | 0_10   |

|    | 9.4    |         | hannels in Unified and Split Modes                                  |        |

|    | 9.5    |         | oprocessor Internal Priority Schemes                                |        |

|    | 0.0    | 9.5.1   | Fixed Priority Scheme                                               |        |

|    |        | 9.5.2   | Rotating Priority Scheme                                            |        |

|    |        | 9.5.3   | Split Mode and DMA Channel Arbitration                              |        |

|    | 9.6    |         | nd DMA Coprocessor Arbitration                                      |        |

|    | 9.7    |         | ransfer Modes                                                       |        |

|    | •••    | 9.7.1   | Running Under TRANSFER MODE = 002                                   |        |

|    |        | 9.7.2   | Running Under TRANSFER MODE = $01_2$                                |        |

|    |        | 9.7.3   | Running Under TRANSFER MODE = 102                                   |        |

|    |        | 9.7.4   | Running Under TRANSFER MODE = 112                                   |        |

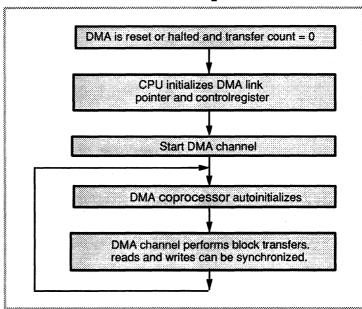

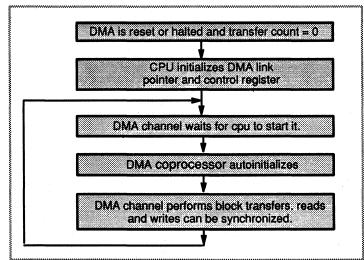

|    | 9.8    | Autoini | tialization                                                         |        |

|    |        | 9.8.1   | Fun With Link Pointers                                              | 9-38   |

|    | 9.9    | DMA C   | oprocessor and Interrupts                                           | 9-40   |

|    |        | 9.9.1   | Interrupts and Synchronization of DMA Channels                      | 9-41   |

|    | 9.10   | TMS32   | 0C40 Timers                                                         |        |

|    |        | 9.10.1  | Timer Global-Control Register                                       | 9-47   |

|    |        | 9.10.2  | Timer Period and Counter Registers                                  | 9-50   |

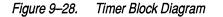

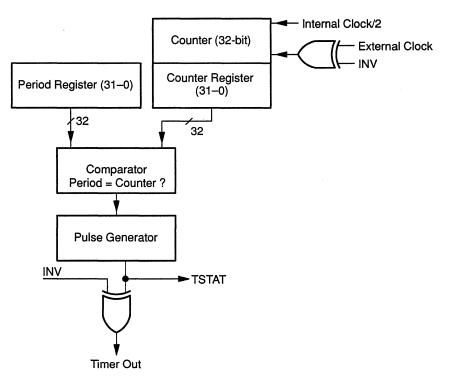

|    |        | 9.10.3  | Timer Pulse Generation                                              | 9-50   |

|    |        | 9.10.4  | Timer Operation Modes                                               | 9-52   |

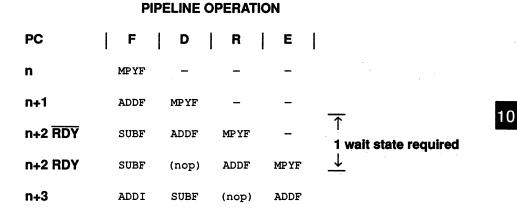

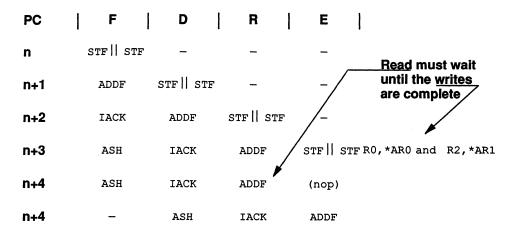

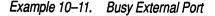

| 10 | Pipeli | ne Ope  | ration                                                              | 10-1   |

|    | 10.1   | Pipelin | e Structure                                                         | 10-2   |

|    | 10.2   | Pipelin | e Conflicts                                                         | 10-4   |

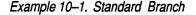

|    |        | 10.2.1  | Branch Conflicts                                                    | 10-4   |

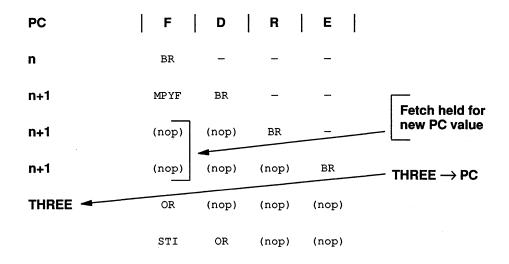

|    |        | 10.2.2  | Register Conflicts                                                  | 10-8   |

|    |        | 10.2.3  | Memory Conflicts                                                    | 10-11  |

|    | 10.3   | Resolv  | ing Memory Conflicts                                                | 10-18  |

|    | 10.4   | Clockin | ng of Memory Accesses                                               | 10-20  |

|    |        | 10.4.1  | Program Fetches                                                     | 10-20  |

|    |        | 10.4.2  | Data Loads and Stores                                               | 10-21  |

| 11 | Assei  | nbly La | Inguage Instructions                                                | . 11-1 |

|    | 11.1   | Assem   | bly Language Instructions — Instruction Set                         |        |

|    |        | 11.1.1  | Load-and-Store Instructions                                         |        |

|    |        | 11.1.2  | Two-Operand Instructions                                            | . 11-4 |

|    |        | 11.1.3  | Three-Operand Instructions                                          | . 11-6 |

|    |       | 11.1.4  | Program Control Instructions                             |         |

|----|-------|---------|----------------------------------------------------------|---------|

|    |       | 11.1.5  | Interlocked Operations Instructions                      | 11-7    |

|    |       | 11.1.6  | Parallel Operations Instructions                         | 11-8    |

|    | 11.2  |         | on Codes and Flags                                       |         |

|    | 11.3  |         | al Instructions                                          |         |

|    |       | 11.3.1  | Symbols and Abbreviations                                |         |

|    |       | 11.3.2  | Optional Assembler Syntaxes                              |         |

|    |       | 11.3.3  | Individual Instruction Descriptions                      | . 11-17 |

| 12 | Softw | are App | lications                                                | 12-1    |

|    | 12.1  | Process | sor Initialization                                       | 12-3    |

|    |       | 12.1.1  | Reset Process                                            | 12-3    |

|    |       | 12.1.2  | Initialization                                           | 12-3    |

|    | 12.2  | Program | m Control                                                | 12-9    |

|    |       | 12.2.1  | Subroutines                                              | 12-9    |

|    |       | 12.2.2  | Software Stack                                           |         |

|    |       | 12.2.3  | Interrupt Service Routines                               | . 12-14 |

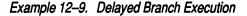

|    |       | 12.2.4  | Delayed Branches                                         | . 12-22 |

|    |       | 12.2.5  | Repeat Modes                                             |         |

|    |       | 12.2.6  | Computed GOTOs to Select Subroutines at Runtime          | . 12-27 |

|    | 12.3  | •       | and Arithmetic Operations                                |         |

|    |       | 12.3.1  | Bit Manipulation                                         | . 12-28 |

|    |       | 12.3.2  | Block Moves                                              |         |

|    |       | 12.3.3  | Byte and Half-Word Manipulation                          | . 12-30 |

|    |       | 12.3.4  | Bit-Reversed Addressing                                  | . 12-31 |

|    |       | 12.3.5  | Integer and Floating-Point Division                      | . 12-33 |

|    |       | 12.3.6  | Square Root                                              |         |

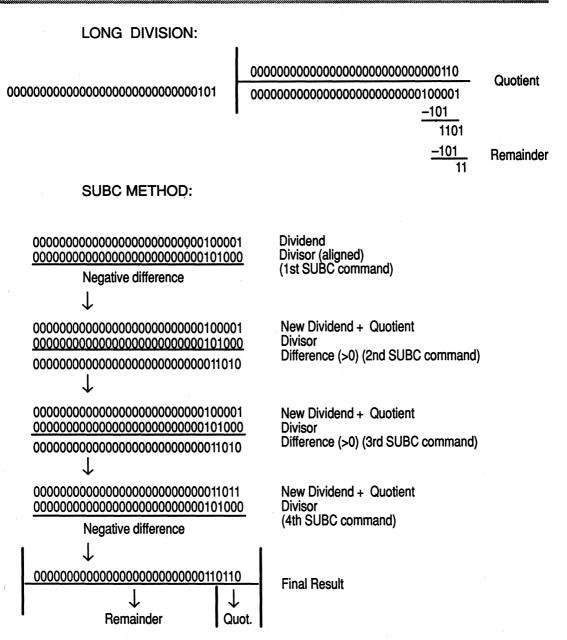

|    |       | 12.3.7  | Extended-Precision Arithmetic                            | . 12-41 |

|    |       | 12.3.8  | Floating-Point Format Conversion: IEEE to/from TMS320C40 | 12-12   |

|    | 12.4  | Applica | tion-Oriented Operations                                 |         |

|    | 16.7  | 12.4.1  | Companding                                               |         |

|    |       |         | FIR, IIR, and Adaptive Filters                           |         |

|    |       |         | Matrix-Vector Multiplication                             |         |

|    |       |         | Fast Fourier Transforms (FFT)                            |         |

|    |       | 12.4.5  | Lattice Filters                                          |         |

|    | 12.5  |         | mming Tips                                               |         |

|    | 12.0  |         | C-Callable Routines                                      |         |

|    |       | 12.5.2  | Hints for Optimizing Assembly Code                       |         |

|    | 12.6  |         | erals                                                    |         |

|    |       |         |                                                          |         |

|    |       |         |                                                          |         |

|    |      | 12.6.2   | Communication Ports                                            | 12-98  |

|----|------|----------|----------------------------------------------------------------|--------|

|    |      | 12.6.3   | Direct Memory Access                                           | 12-101 |

|    |      |          |                                                                |        |

| 13 |      |          | plications                                                     |        |

|    | 13.1 | •        | Configuration Options Overview                                 |        |

|    |      |          | Categories of Interfaces on the TMS320C40                      |        |

|    | 13.2 |          | bader Description and External ROM Interfacing                 |        |

|    |      | 13.2.1   | TMS320C40 Boot Loader Description/Operation                    |        |

|    |      | 13.2.2   | Boot Load Sequence                                             |        |

|    |      | 13.2.3   |                                                                |        |

|    |      | 13.2.4   | Communication Port Loading                                     |        |

|    |      | 13.2.5   | External ROM Interfacing to the TMS320C40                      |        |

|    |      | 13.2.6   | IIOF(3–1) Pin Loading                                          |        |

|    |      | 13.2.7   | TMS320C40 Boot Loader Source Program                           |        |

|    | 13.3 |          | and Local Bus Interface                                        |        |

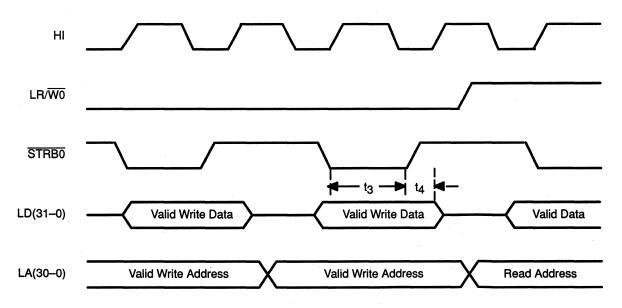

|    |      | 13.3.1   | Zero Wait-State Interface to RAMs                              |        |

|    | 13.4 |          | ates and Ready Generation                                      |        |

|    |      | 13.4.1   | ORing of the Ready Signals (STRBx SWW = 10)                    |        |

|    |      | 13.4.2   |                                                                |        |

|    |      | 13.4.3   |                                                                |        |

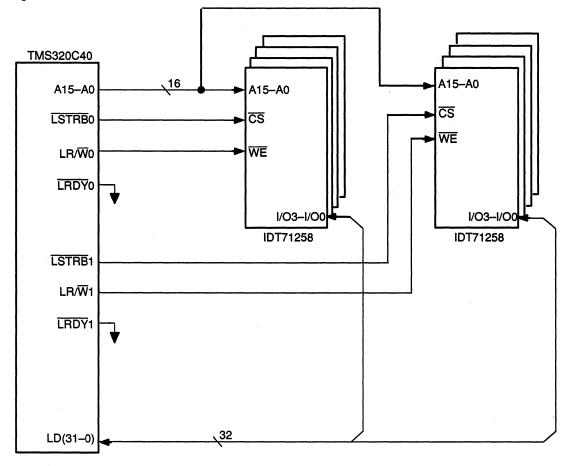

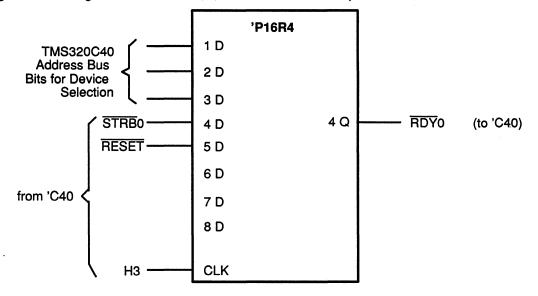

|    |      | 13.4.4   | Ready Control Logic                                            | 13-30  |

|    |      | 13.4.5   | Example Circuit                                                | 13-31  |

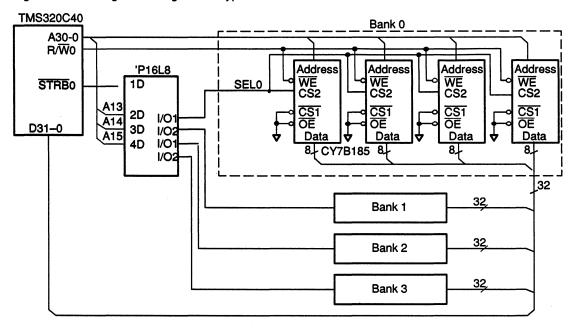

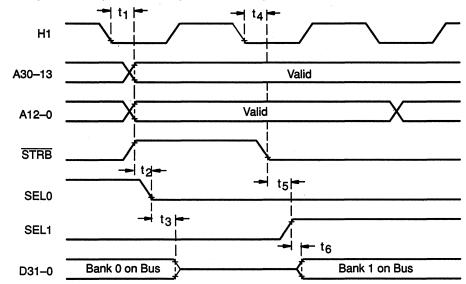

|    |      | 13.4.6   | Page Switching Techniques                                      | 13-32  |

|    | 13.5 | Paralle  | I Processing Interfaces                                        | 13-37  |

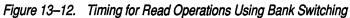

|    |      | 13.5.1   | Message Broadcasting From One TMS320C40<br>to Many TMS320C40's | 13-37  |

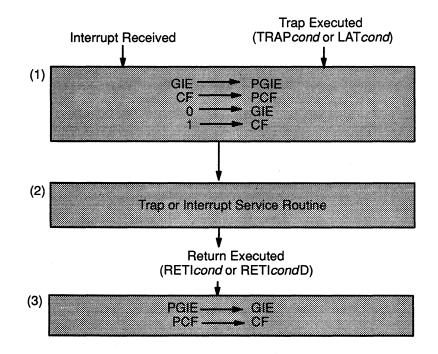

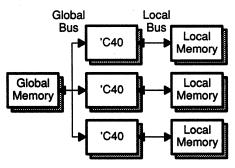

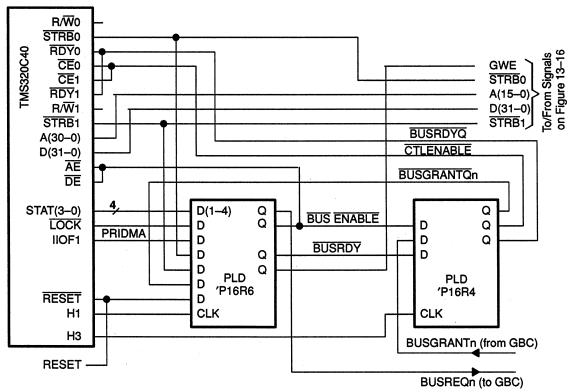

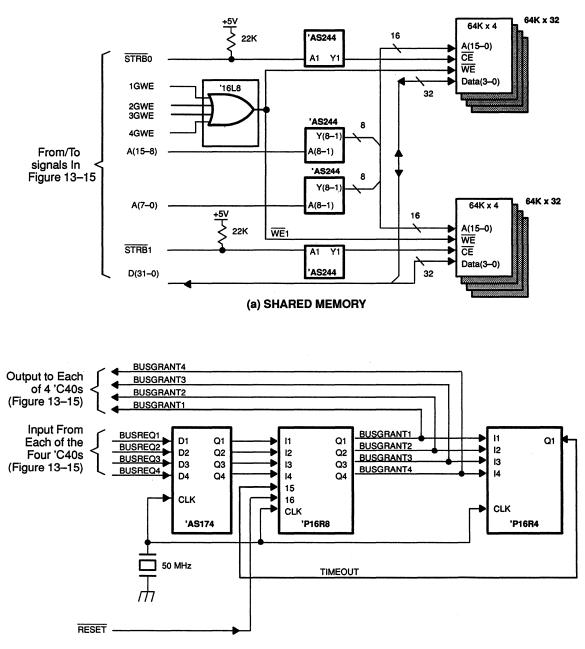

|    |      | 13.5.2   | Shared Global Memory Interface With Fair Bus Arbitration       | 13-38  |

|    |      | 13.5.3   | Shared Bus Interface Overview                                  | 13-43  |

|    | 13.6 | Bus Art  | pitration                                                      | 13-48  |

|    |      | 13.6.1   | Arbitration Implementation                                     | 13-48  |

|    |      | 13.6.2   | Arbitration Alternatives                                       | 13-70  |

|    |      | 13.6.3   | Global Bus Arbitration and Transfer Timing                     | 13-70  |

|    |      | 13.6.4   | Arbitration Protocol Limitations                               |        |

|    | 13.7 | Reset S  | Signal Generation Control Function                             | 13-75  |

| 14 | TMS3 | 20C4x S  | Signal Descriptions and Electrical Characteristics             | . 14-1 |

|    | 14.1 |          | and Pin Assignments                                            |        |

|    | 14.2 | Signal I | Descriptions                                                   | . 14-7 |

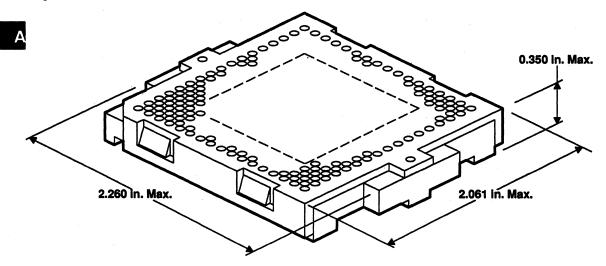

|    | 14.3 |          | 0C4x Mechanical Data                                           |        |

|    | 14.4 |          | al Specifications                                              |        |

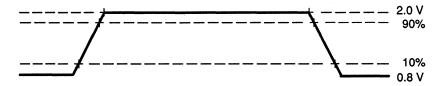

|    |      |          | Transition Levels                                              |        |

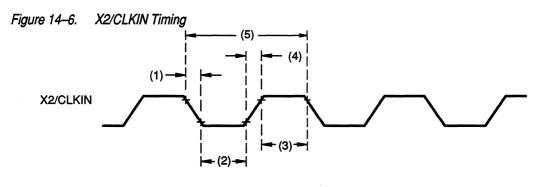

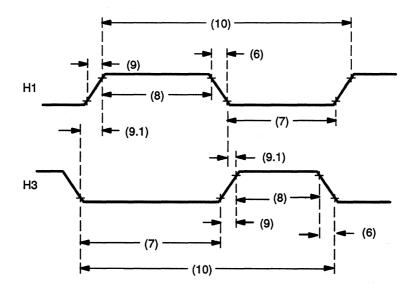

|     | 14.6 | Timing                                  | 15  |

|-----|------|-----------------------------------------|-----|

| A   | TMS3 | 20C4x Sockets                           | -1  |

|     | A.1  | Tool-Activated ZIF PGA Socket (TAZ) A   | -2  |

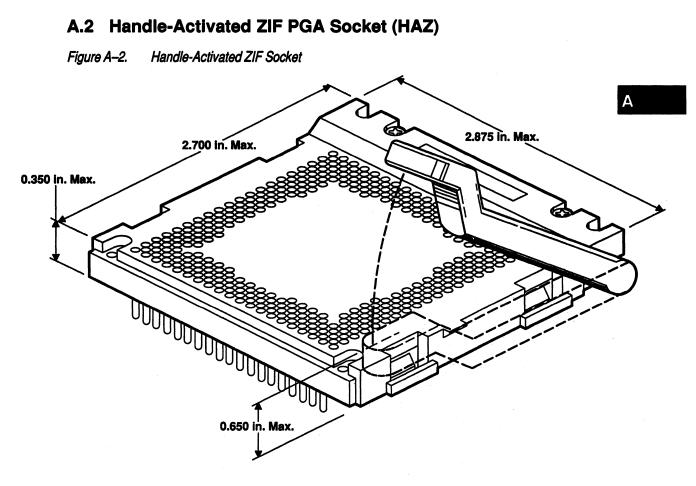

|     | A.2  | Handle-Actuated ZIF PGA Socket (HAZ) A  |     |

| в   | XDS5 | 10 Design Considerations B              | -1  |

|     | B.1  | Header and Header Signals B             | -2  |

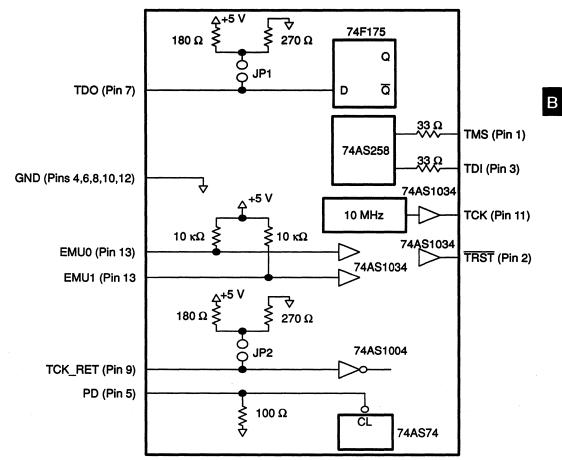

|     | B.2  | Bus Protocol                            | -3  |

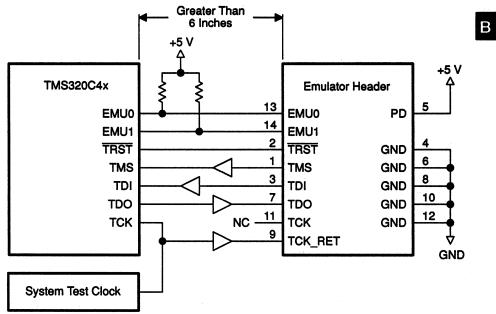

|     | B.3  | Cable Pod B                             | -4  |

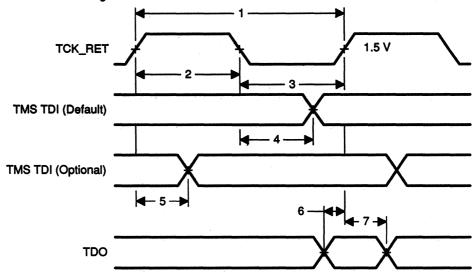

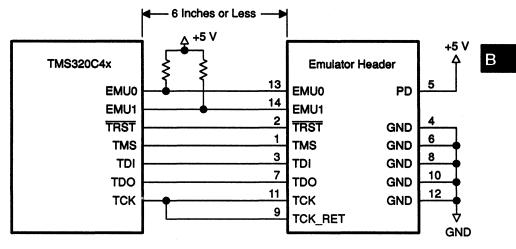

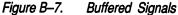

|     | B.4  | Test Clock Generated in Target System B | -7  |

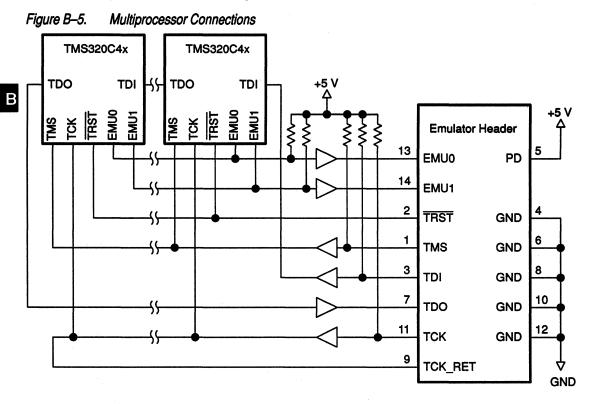

|     | B.5  | Multiprocessor Configuration            |     |

|     | B.6  | Emulation Timing Calculations B-        |     |

| Ind | ex   | Index                                   | :-1 |

# Figures

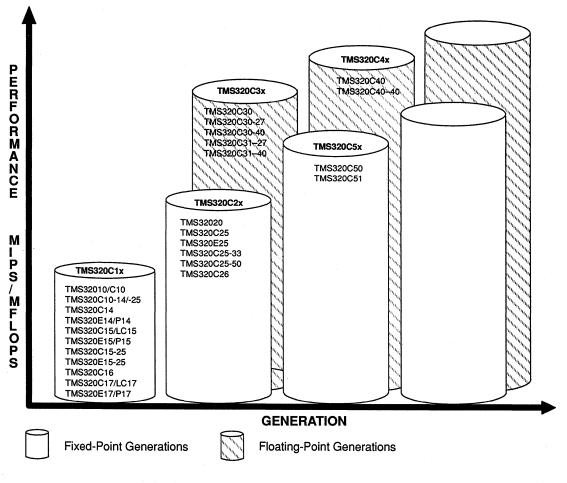

| 1—1  | TMS320 Family of Devices 1-2                                  |

|------|---------------------------------------------------------------|

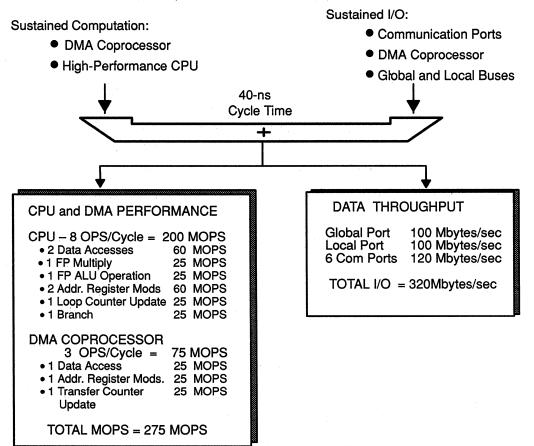

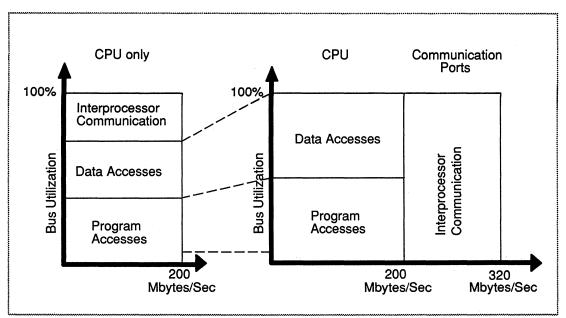

| 1–2  | TMS320C40 Throughput Increases Use of Communication Ports 1-7 |

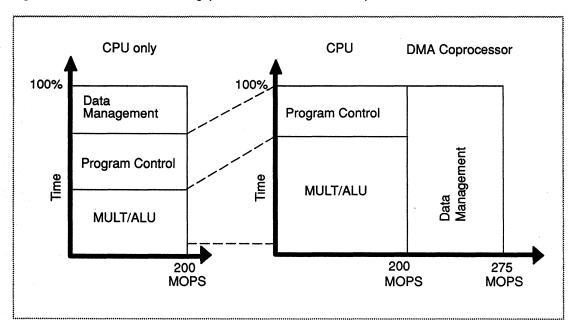

| 1–3  | TMS320C40 Throughput Increases Use of DMA Coprocessor         |

| 1-4  | Matrix of TMS320 DSP Applications                             |

| 2-1  | TMS320C40 Block Diagram                                       |

| 2-2  | Central Processing Unit (CPU)                                 |

| 2–3  | Memory Organization                                           |

| 2–4  | Memory Maps                                                   |

| 2–5  | Peripheral Memory Map 2-14                                    |

| 2–6  | Peripheral Modules                                            |

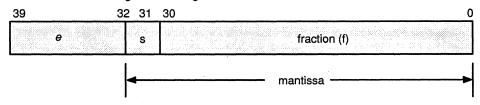

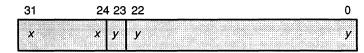

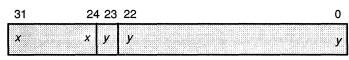

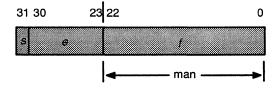

| 3–1  | Extended-Precision Register Floating-Point Format             |

| 3–2  | Extended-Precision Register Integer Format                    |

| 3–3  | Status Register                                               |

| 3–4  | DMA Interrupt Enable Register Bit Functions                   |

| 3–5  | Internal Interrupt Enable Register (IIE)                      |

| 3–6  | Interrupt Flag Register (IIF)                                 |

| 3–7  | Trap Vector Table (TVT)                                       |

| 3–8  | Interrupt-Vector Table (IVT)                                  |

| 3–9  | Memory Maps                                                   |

| 3–10 | Peripheral Memory Map 3-20                                    |

| 3–11 | Memory Interface Control Registers                            |

| 3–12 | Analysis Module Registers                                     |

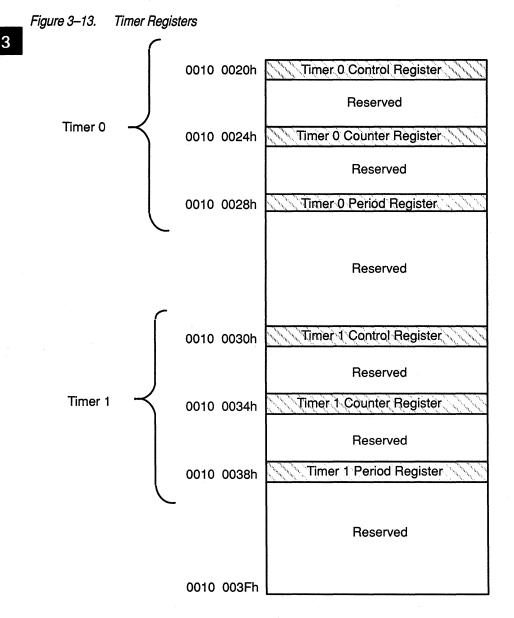

| 3–13 | Timer Registers                                               |

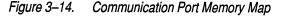

| 3–14 | Communication Port Memory Map 3-23                            |

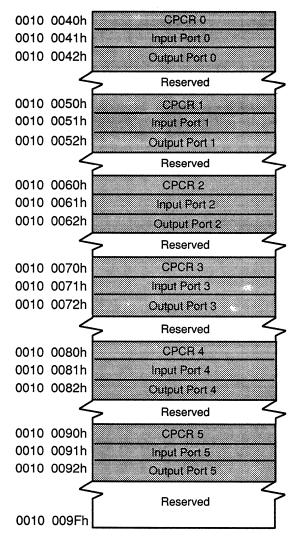

| 3–15 | DMA Coprocessor Memory Map 3-24                               |

| 3–16 | Address Partitioning for Cache Control Algorithm              |

| 3–17 | Instruction Cache Architecture                                |

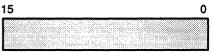

| 4—1  | Short Integer Format and Sign Extension of Short Integer      |

| 4–2  | Single-Precision Integer Format                               |

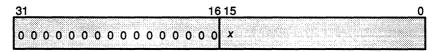

| 4-3        | Short Unsigned-Integer Format and Zero Fill                            | . 4-4 |

|------------|------------------------------------------------------------------------|-------|

| 4-4        | Single-Precision Unsigned-Integer Format                               | . 4-4 |

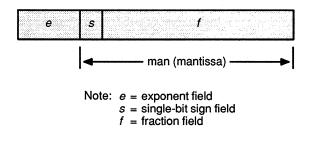

| 4-5        | Generic Floating-Point Format                                          |       |

| 46         | Short Floating-Point Format                                            | . 4-6 |

| 4-7        | Single-Precision Floating-Point Format                                 | . 4-7 |

| 48         | Extended-Precision Floating-Point Format                               | . 4-8 |

| 49         | IEEE Single-Precision Std. 754 Floating-Point Format                   | 4-11  |

| 4–10       | TMS320C4x Single-Precision Twos-Complement Floating-Point<br>Format    | 1-11  |

| 4-11       | Flowchart for Floating-Point Multiplication                            |       |

| 4-12       | Flowchart for Floating-Point Addition                                  |       |

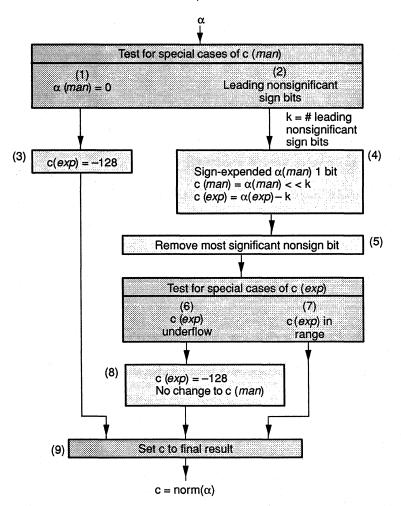

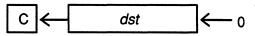

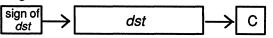

| 4-13       | Flowchart for NORM Instruction Operation                               |       |

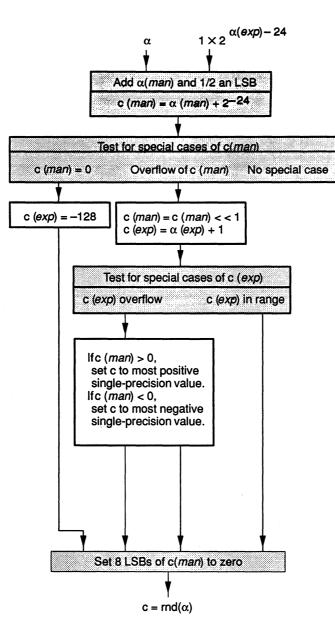

| 4-14       | Flowchart for Floating-Point Rounding by the RND Instruction           |       |

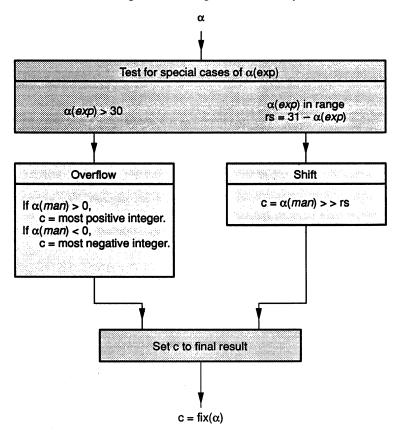

| 4-15       | Flowchart for Floating-Point-to-Integer Conversion by FIX Instructions |       |

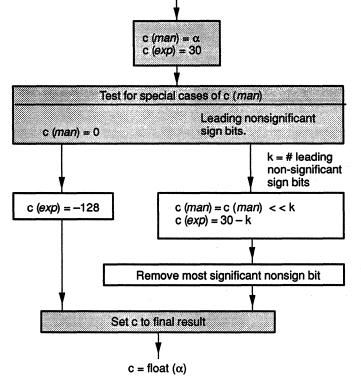

| 4-16       | Flowchart for Integer-to-Floating-Point Conversion by FLOAT            | 0     |

|            | Instructions                                                           | 4-30  |

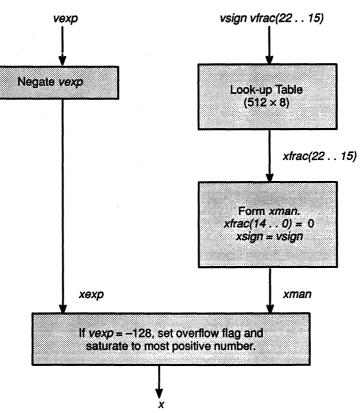

| 4–17       | RCPF Instruction Algorithm                                             | 4-31  |

| 4–18       | Newton-Raphson Algorithm for Computing the Reciprocal                  | 4-32  |

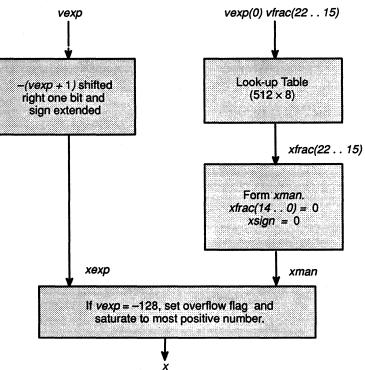

| 4–19       | RSQRF Instruction Algorithm                                            | 4-33  |

| 4-20       | Newton-Raphson Algorithm for Computing the Reciprocal                  |       |

|            | Square Root                                                            |       |

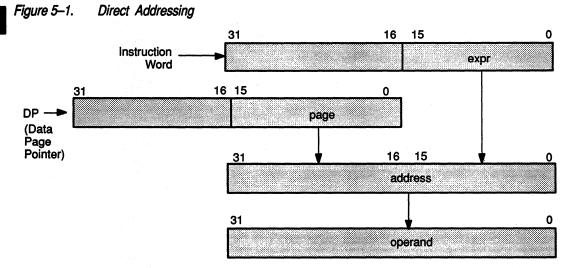

| 5-1        | Direct Addressing                                                      |       |

| 5–2        | Encoding for 24-Bit PC-Relative Addressing Mode                        |       |

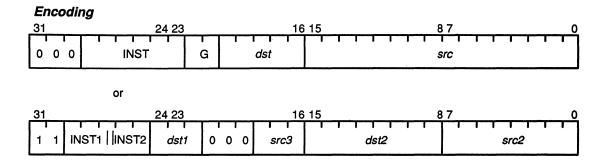

| 53         | Encoding for General Addressing Modes                                  | 5-20  |

| 5-4        | Encoding for Type 1 Three-Operand Addressing Modes<br>('C30 and 'C40)  | E 00  |

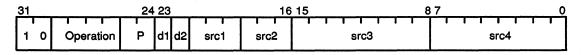

| 5-5        | Encoding for Type 2 Three-Operand Addressing Modes ('C40 Only)         |       |

| 5-6        | Encoding for Parallel Addressing Modes                                 |       |

| 5–0<br>5–7 | Encoding for Conditional-Branch Addressing Modes                       |       |

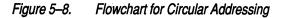

| 58         | Flowchart for Circular Addressing                                      |       |

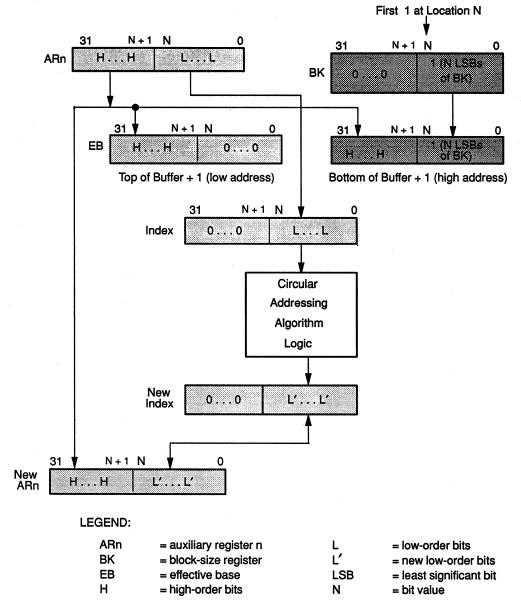

| 5-0<br>5-9 | Circular Buffer Implementation                                         |       |

| 5–10       |                                                                        |       |

| 5-10       | Circular Addressing Example                                            |       |

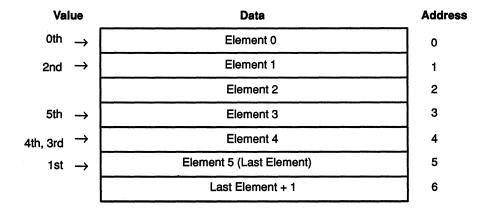

|            | Data Structure for FIR Filters                                         |       |

| 5-12       | FIR Filter Code Using Circular Addressing                              |       |

| 5-13       | Bit-Reversed Addressing Example                                        |       |

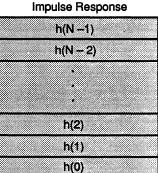

| 5–14       | System Stack Configuration                                             | 5-31  |

| 5–15 | Implementations of High-to-Low Memory Stacks                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------|

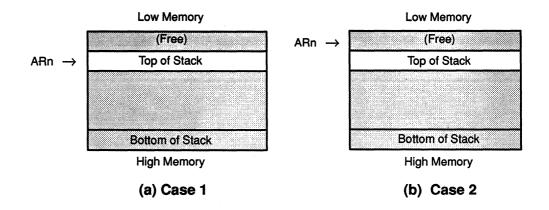

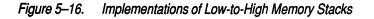

| 5–16 | Implementations of Low-to-High Memory Stacks                                                                    |

| 6—1  | Repeat-Mode Control Algorithm                                                                                   |

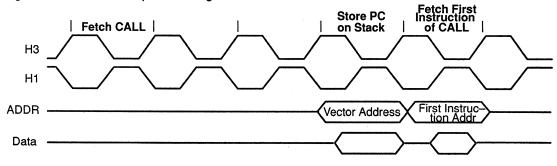

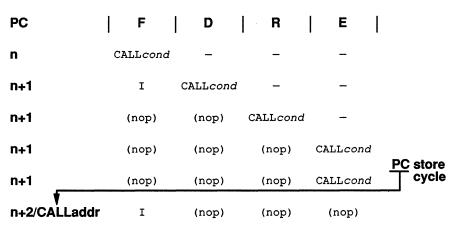

| 6–2  | CALL Response Timing                                                                                            |

| 6–3  | Unified Flow of Traps and Interrupts                                                                            |

| 64   | Multiple TMS320C40s Sharing Global Memory                                                                       |

| 6–5  | Interrupt-Vector Table (IVT)                                                                                    |

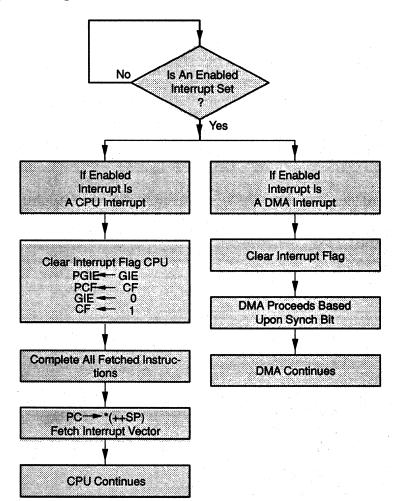

| 6–6  | Interrupt Processing                                                                                            |

| 7–1  | Global and Local Memory Interface Control Signals                                                               |

| 7-2  | Format for the Memory-Interface Control Registers                                                               |

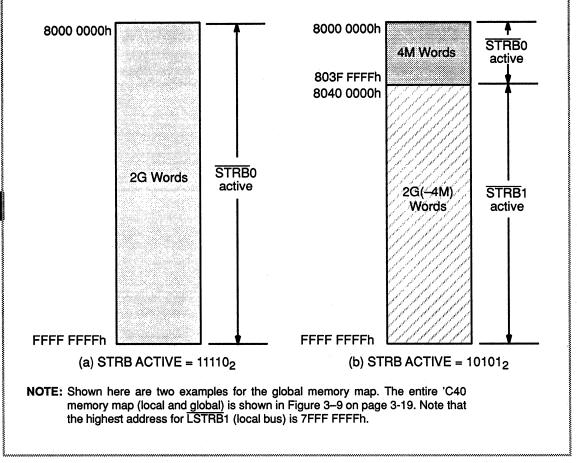

| 7–3  | Effects of STRB ACTIVE on Global Memory Bus Memory Map                                                          |

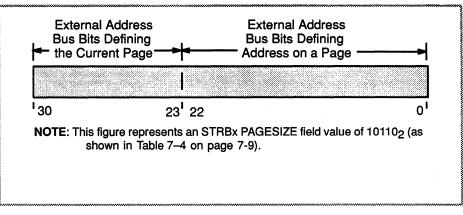

| 7–4  | STRBx PAGESIZE Fields Example                                                                                   |

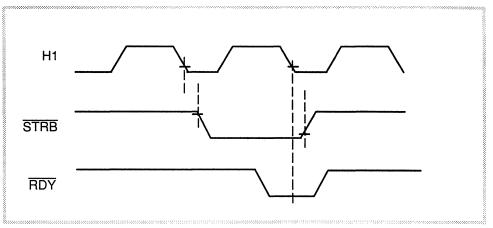

| 7–5  | STRB and RDY Timing                                                                                             |

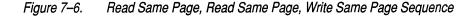

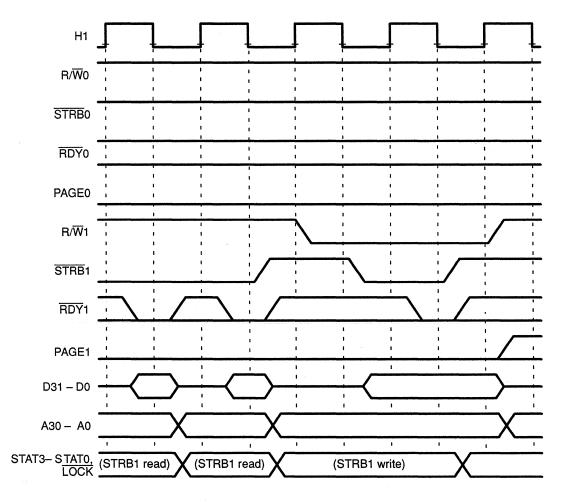

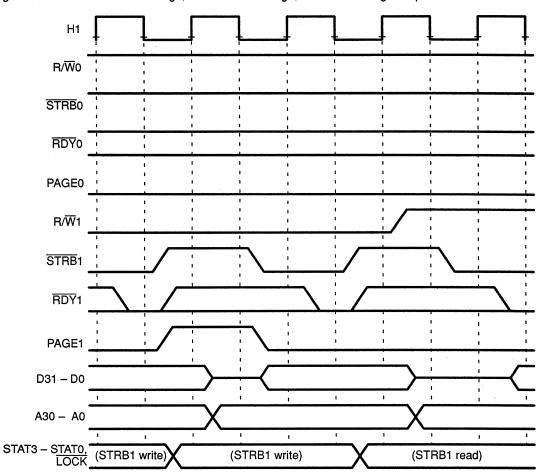

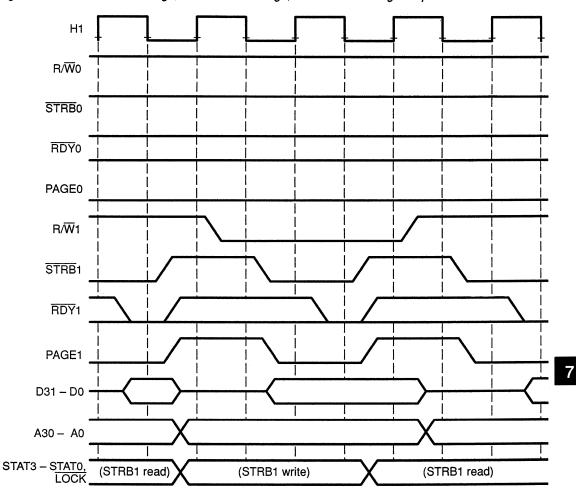

| 7–6  | Read Same Page, Read Same Page, Write Same Page Sequence 7-18                                                   |

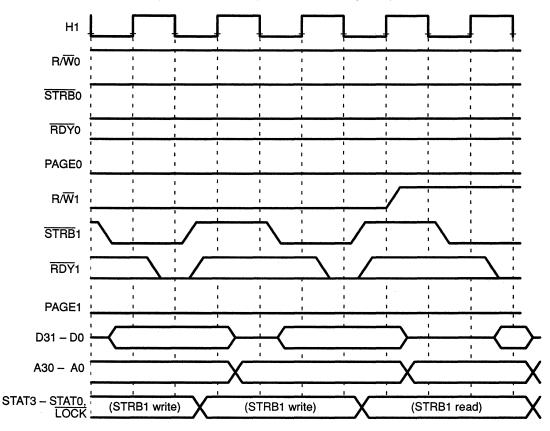

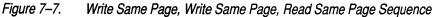

| 7–7  | Write Same Page, Write Same Page, Read Same Page Sequence 7-19                                                  |

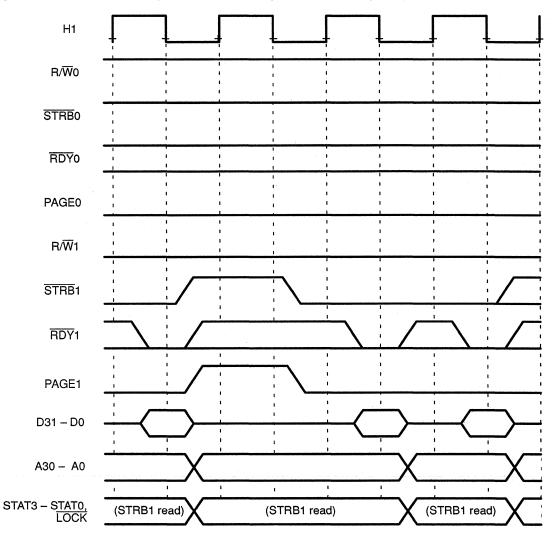

| 7–8  | Read Same Page, Read Different Page, Read Same Page Sequence 7-20                                               |

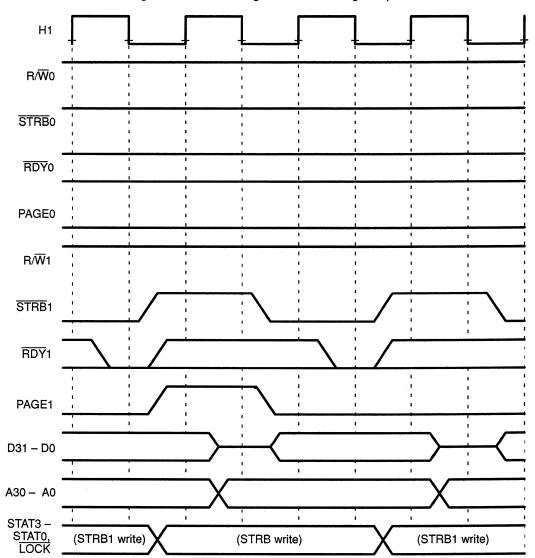

| 7–9  | Write Same Page, Write Different Page, Write Same Page Sequence 7-21                                            |

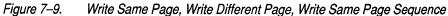

| 7–10 | Write Same Page, Read Different Page, Write Different Page<br>Sequence                                          |

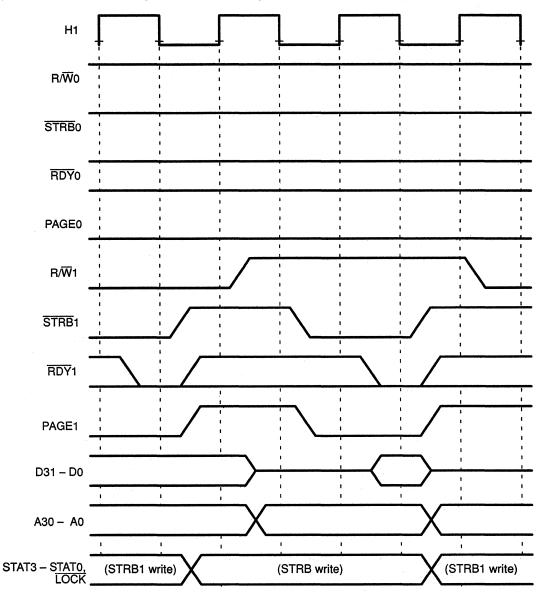

| 7–11 | Read Different Page, Read Different Page, Write Same Page                                                       |

|      | Sequence                                                                                                        |

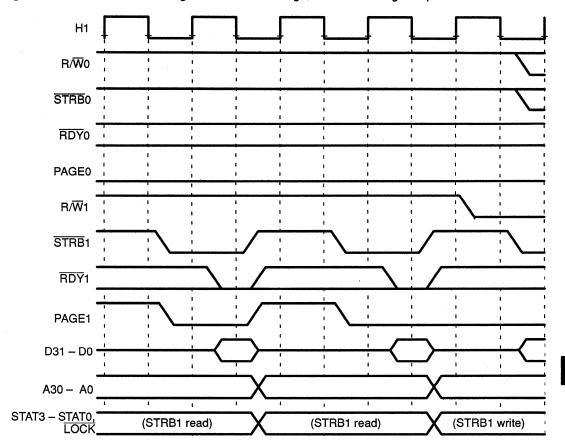

| 7–12 | Write Different Page, Write Different Page, Read Same Page      Sequence      7-24                              |

| 7–13 | Read Same Page, Write Different Page, Read Different Page                                                       |

|      | Sequence                                                                                                        |

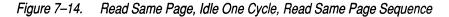

| 7–14 | Read Same Page, Idle One Cycle, Read Same Page Sequence                                                         |

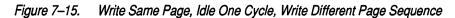

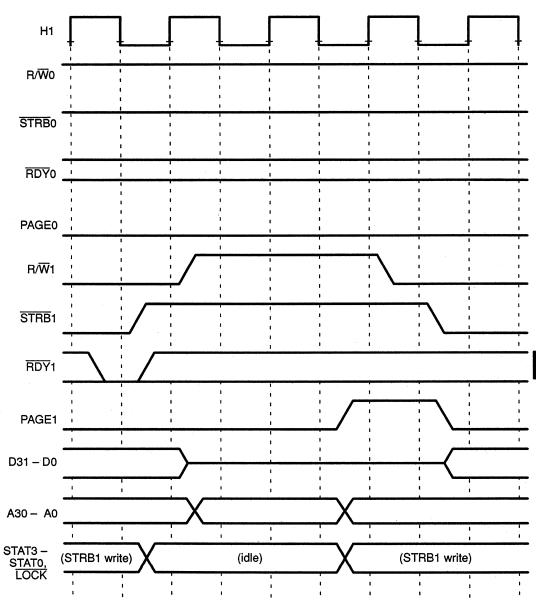

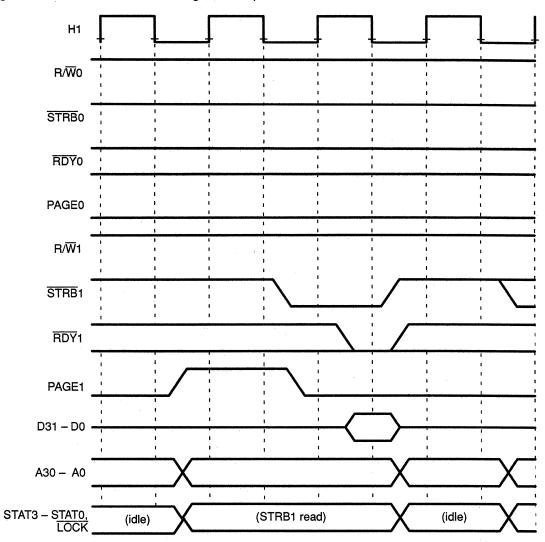

| 7–15 | Write Same Page, Idle One Cycle, Write Different Page Sequence 7-27                                             |

| 7–16 | Idle, Read Different Page, Idle Sequence                                                                        |

| 7–17 | Idle, Write Same Page, Idle Sequence                                                                            |

| 7–18 | Write Different or Same Page, Idle, Idle Sequence                                                               |

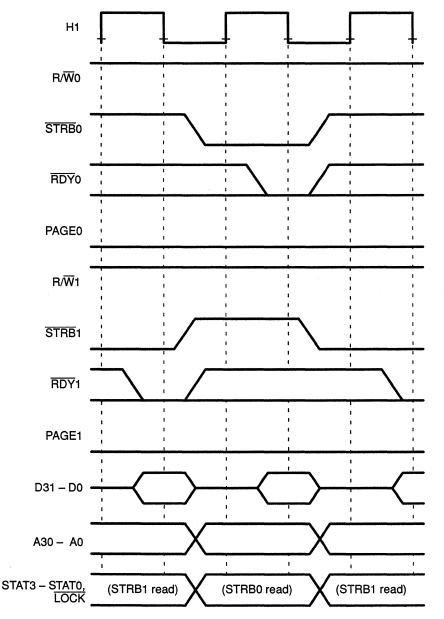

| 7–19 | Read Same Page on STRB1, Read Same Page on STRB0, Read<br>Same Page on STRB1 Sequence When STRB SWITCH = 0      |

| 7–20 | Read Same Page on STRB1, Read Same Page on STRB0, Read<br>Same Page on STRB1 Sequence When STRB SWITCH = 1      |

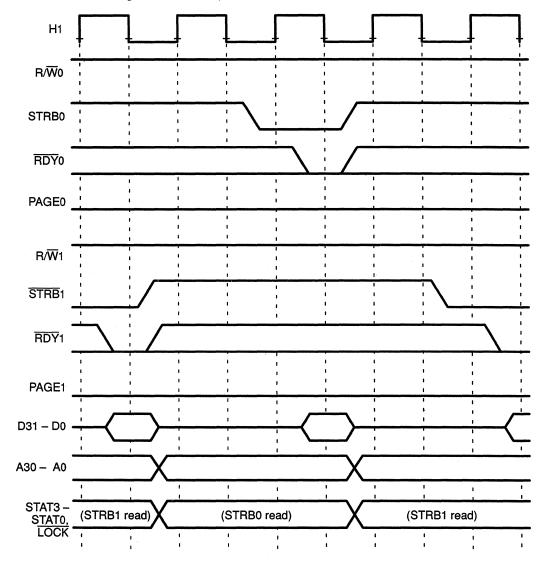

| 7–21 | Read Same Page on STRB1, Read Same Page on STRB0, Read<br>Different Page on STRB1 Sequence When STRB SWITCH = 0 |

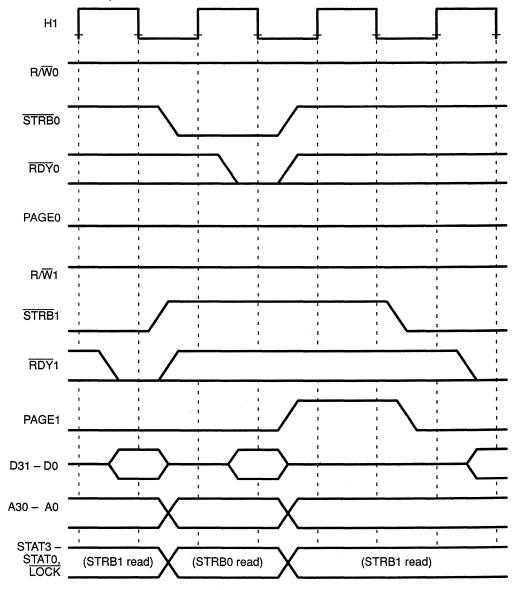

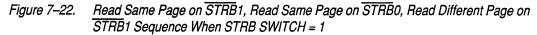

| 7–22 | Read Same Page on STRB1, Read Same Page on STRB0,<br>Read Different Page on STRB1 Sequence When STRB SWITCH = $1 \dots 7-34$                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|

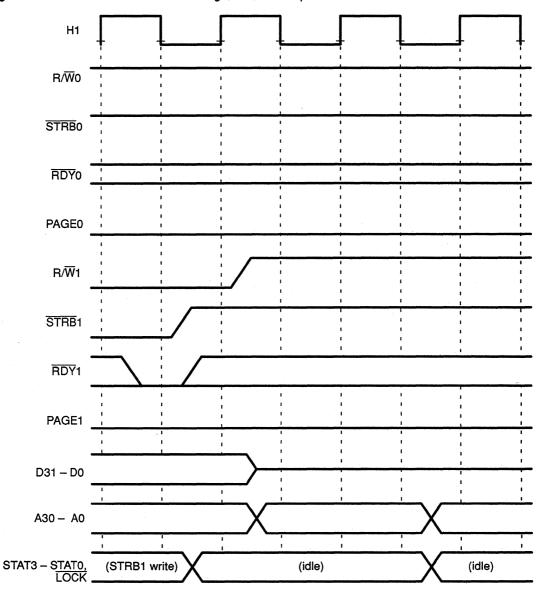

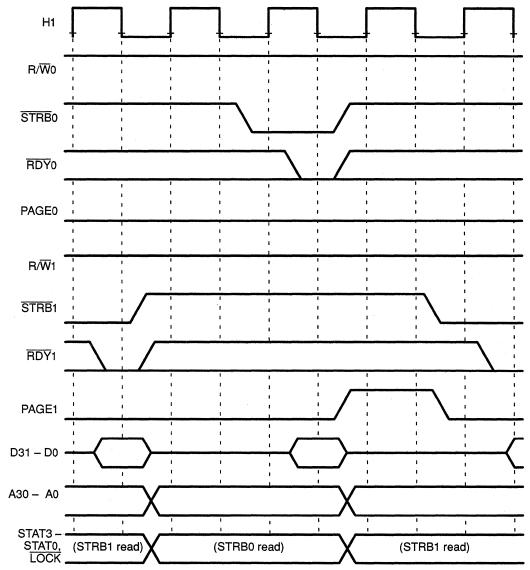

| 7–23 | Write Same Page on STRB1, Write Same Page on STRB0,Read Same Page on STRB1 Sequence7-35                                                        |

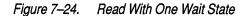

| 7–24 | Read With One Wait State                                                                                                                       |

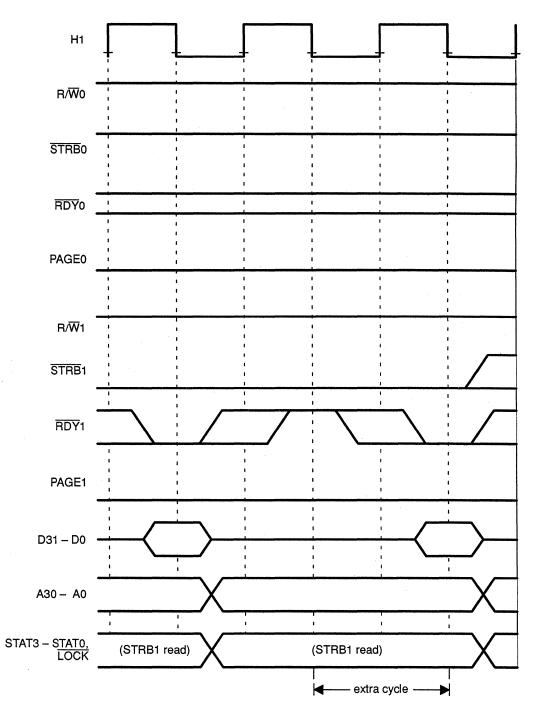

| 7–25 | Write With One Wait State                                                                                                                      |

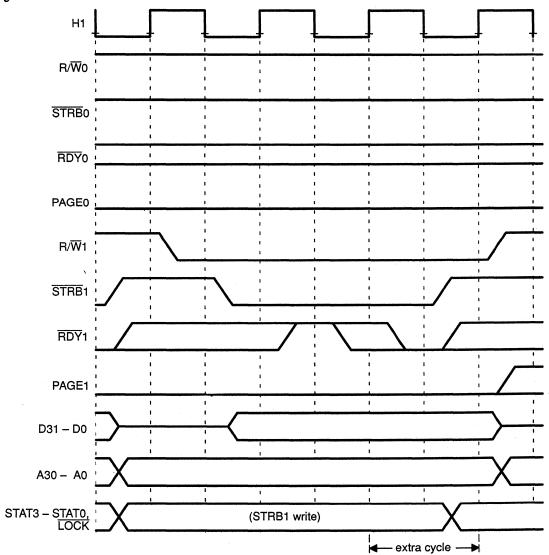

| 7–26 | Using Enabled Signals to Put Signal Groups in a High-Impedance<br>State                                                                        |

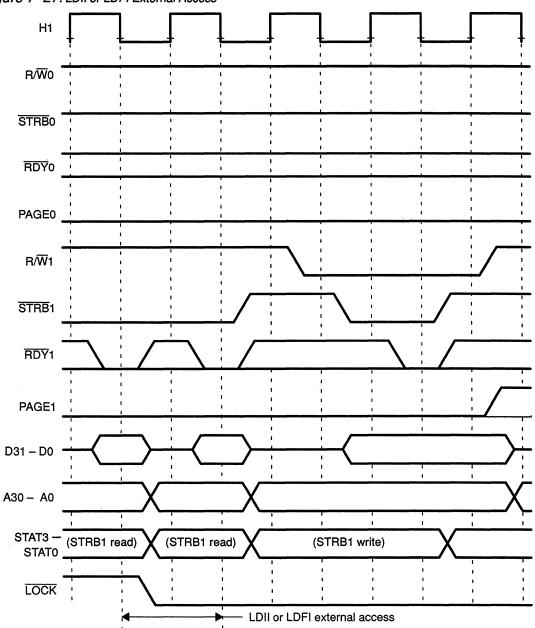

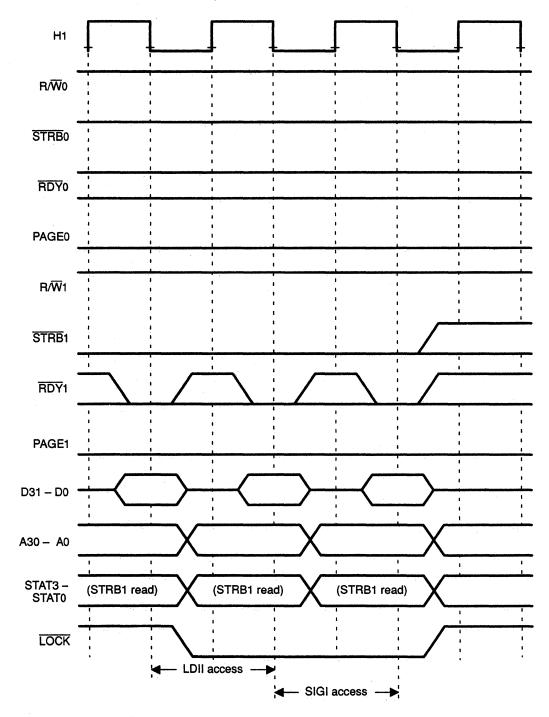

| 7–27 | LDII or LDFI External Access                                                                                                                   |

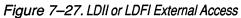

| 7–28 | STII or STFI External Access                                                                                                                   |

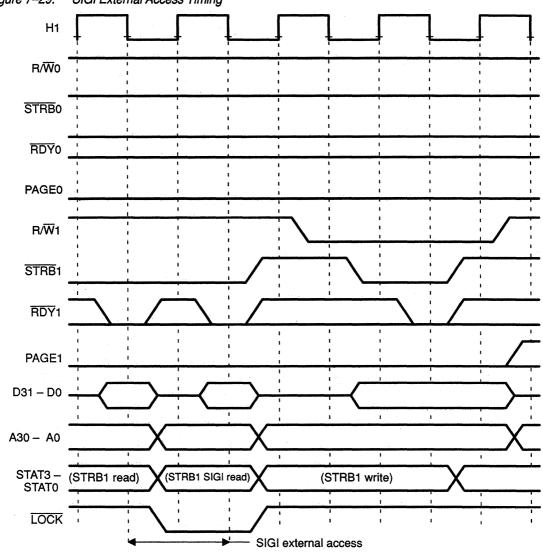

| 7–29 | SIGI External Access Timing                                                                                                                    |

| 7–30 | SIGI When LOCK Is Already Low                                                                                                                  |

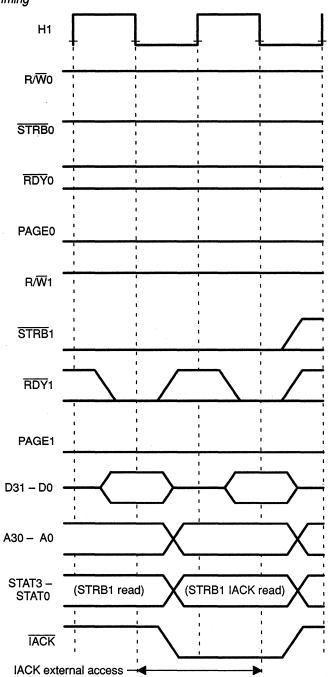

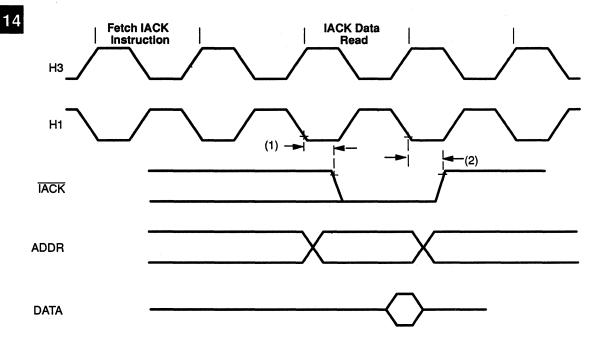

| 7–31 | IACK Timing         7-48                                                                                                                       |

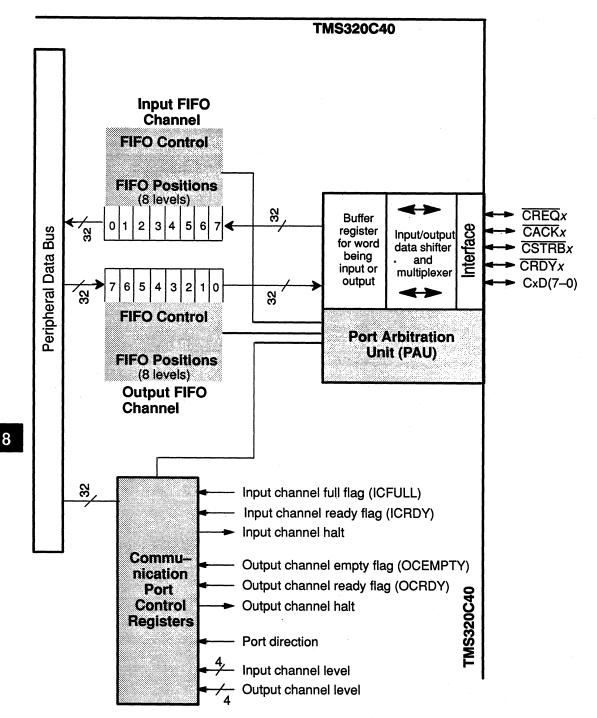

| 8—1  | Communication Port Block Diagram                                                                                                               |

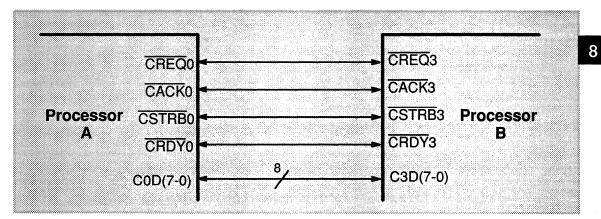

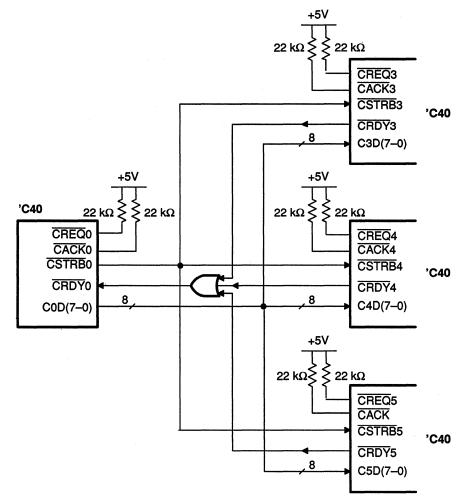

| 8–2  | TMS320C40 Communication-Port Interface-Connection Example                                                                                      |

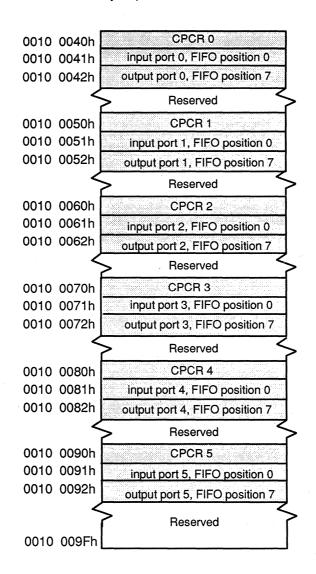

| 8–3  | Communication Port Memory Map 8-8                                                                                                              |

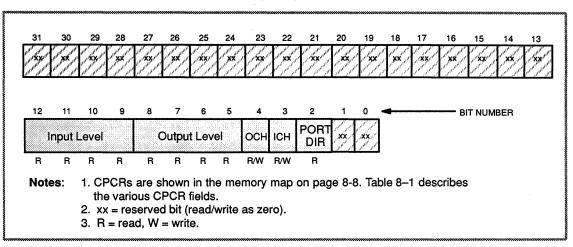

| 8-4  | Communication Port Control Register (CPCR)                                                                                                     |

| 8–5  | Communication Port Arbitration Unit State Diagram                                                                                              |

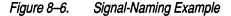

| 86   | Signal-Naming Example                                                                                                                          |

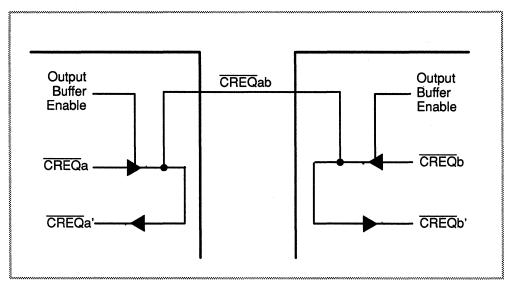

| 8–7  | Token Transfer Sequence    8-23                                                                                                                |

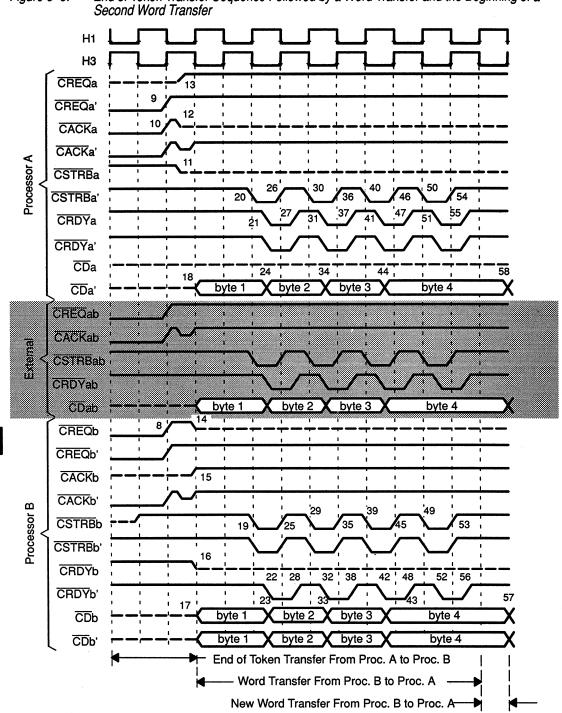

| 8–8  | End of Token Transfer Sequence Followed by a Word Transfer and the Beginning of a Second Word Transfer                                         |

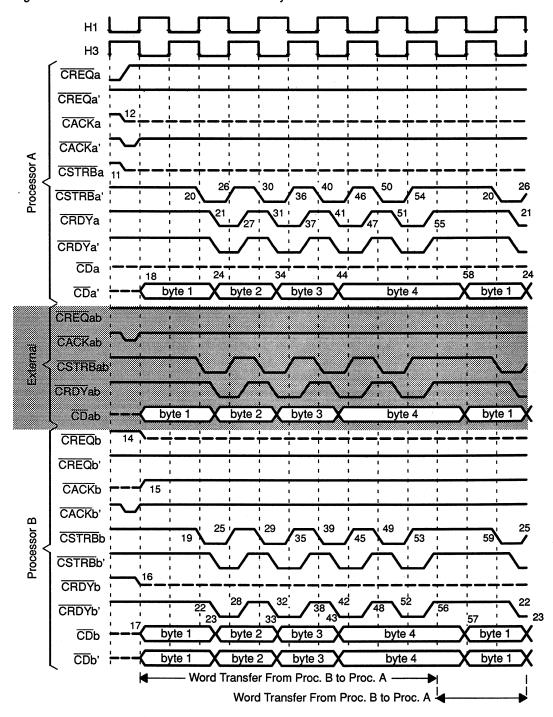

| 8–9  | End of a Word Transfer Followed by a Word Transfer                                                                                             |

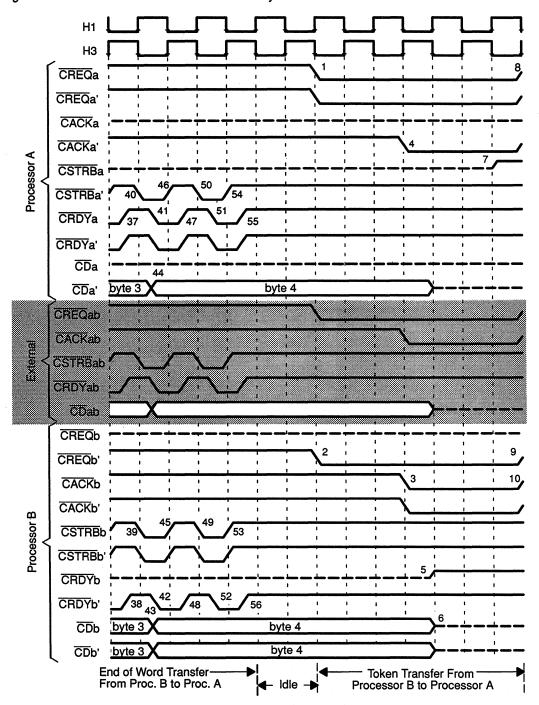

| 8–10 | End of a Word Transfer Followed by an Idle State and Token Transfer 8-26                                                                       |

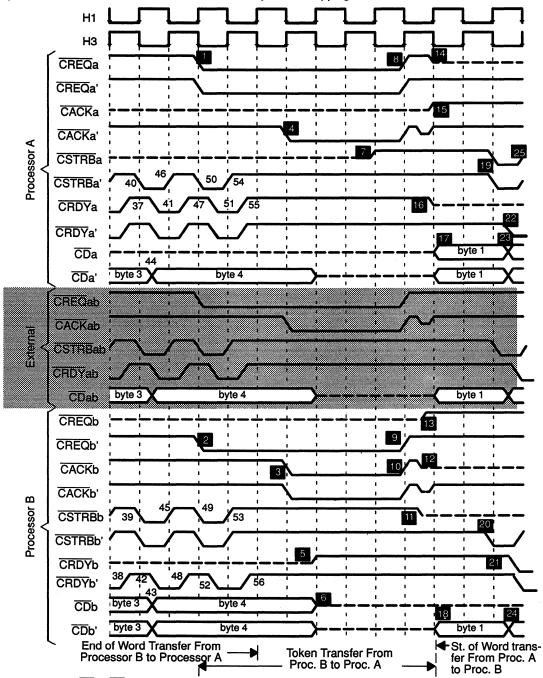

| 8–11 | End of a Word Transfer Followed by an Overlapping Token Transfer 8-27                                                                          |

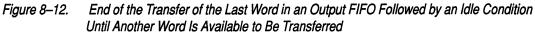

| 8–12 | End of the Transfer of the Last Word in an Output FIFO Followed by<br>an Idle Condition Until Another Word Is Available to Be Transferred 8-28 |

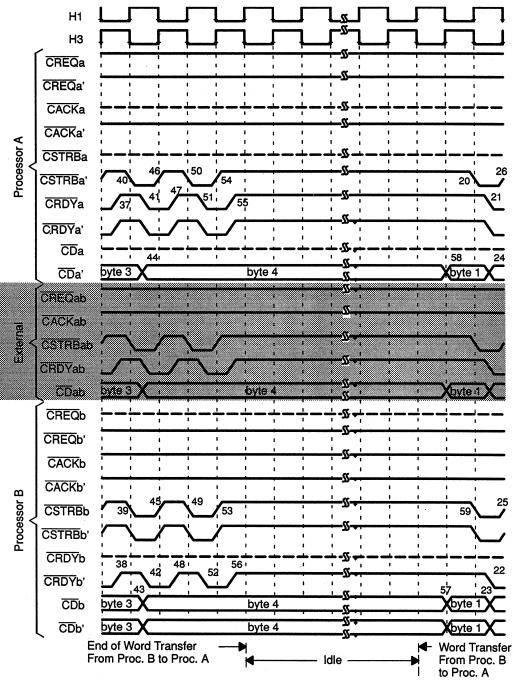

| 8–13 | End of a Word Transfer Followed by a Not Ready Due to the Input FIFO<br>Becoming Full, Continuing Once the Input FIFO Is No Longer Full 8-29   |

| 8–14 | Post-Reset State for an Output Port                                                                                                            |

| 8–15 | Post-Reset State for an Input Port                                                                                                             |

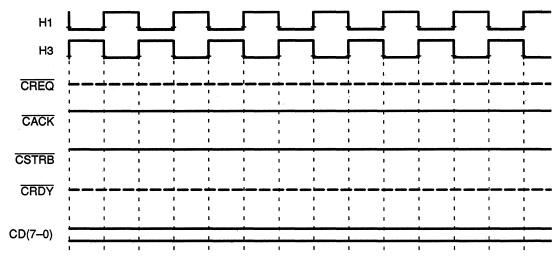

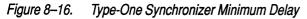

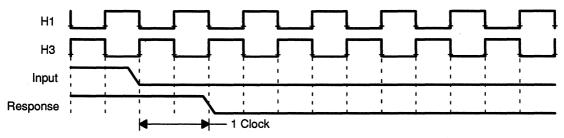

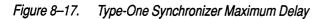

| 8–16 | Type-One Synchronizer Minimum Delay         8-31                                                                                               |

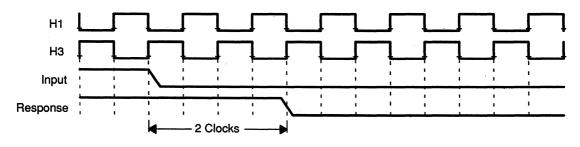

| 8–17 | Type-One Synchronizer Maximum Delay    8-31                                                                                                    |

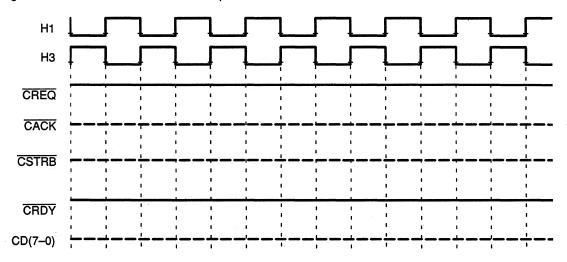

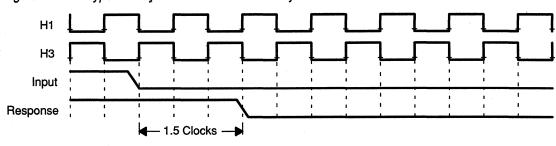

| 8–18 | Type-Two Synchronizer Minimum Delay    8-32                                                                                                    |

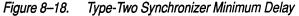

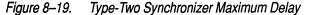

| 8–19 | Type-Two Synchronizer Maximum Delay                                                                                                            |

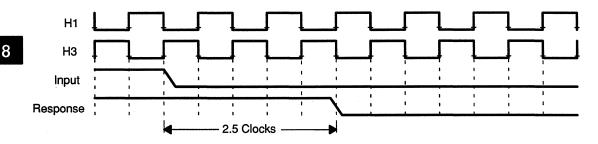

| 9–1  | DMA Coprocessor Memory Map                                                                                                                     |

| 9–2              | Subsections Where DMA Channel Registers Are Described                                                                     | 9-5  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|------|

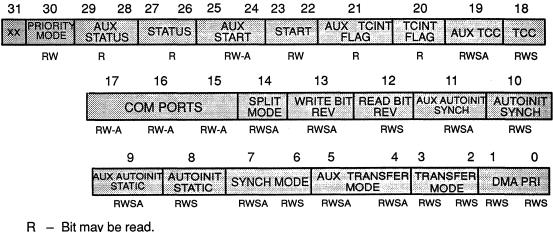

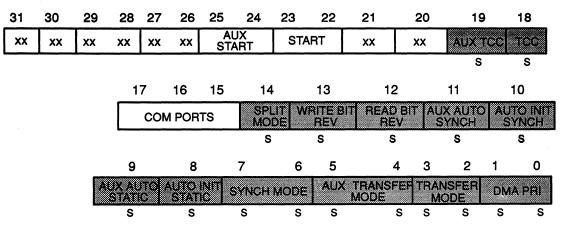

| 9–3              | DMA Channel Control Register                                                                                              | 9-8  |

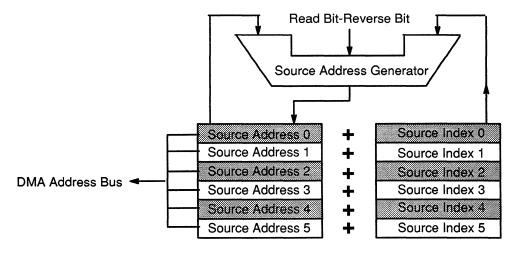

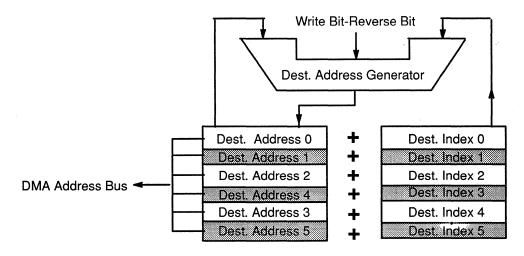

| 9-4              | DMA-Coprocessor Address Generation                                                                                        | 9-17 |

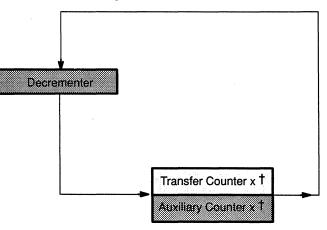

| 95               | DMA Coprocessor Transfer-Count Registers                                                                                  | 9-18 |

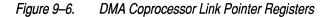

| 96               | DMA Coprocessor Link Pointer Registers                                                                                    | 9-19 |

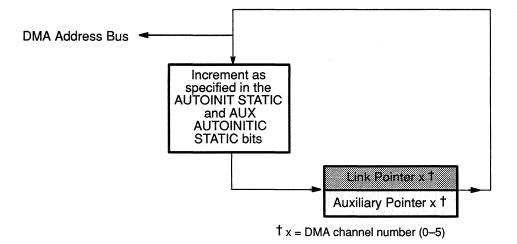

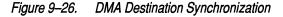

| <del>9</del> –7  | Typical Unified Mode DMA Channel Configuration                                                                            | 9-21 |

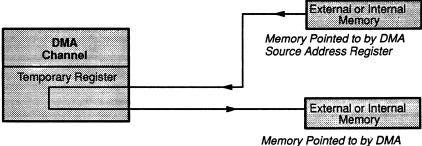

| 98               | Typical Split-Mode DMA Configuration                                                                                      | 9-21 |

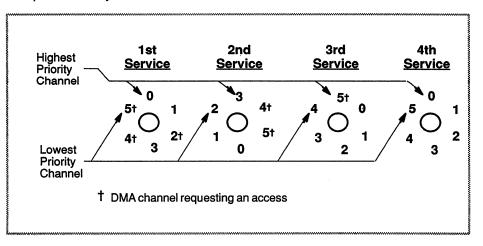

| 9–9              | Rotating Priority Mode Example of the DMA Coprocessor                                                                     | 9-23 |

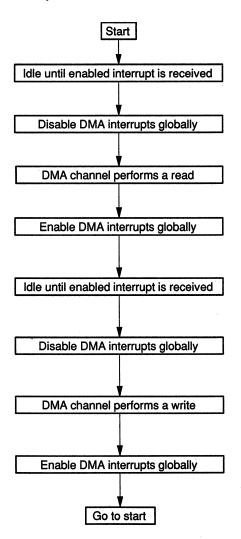

| 9–10             | DMA Read and Write Sequence Example                                                                                       | 9-23 |

| 9–11             | Example of a Priority Wheel                                                                                               | 9-24 |

| 9–12             | Example of a Channel Priority Scheme in Split Mode                                                                        | 9-25 |

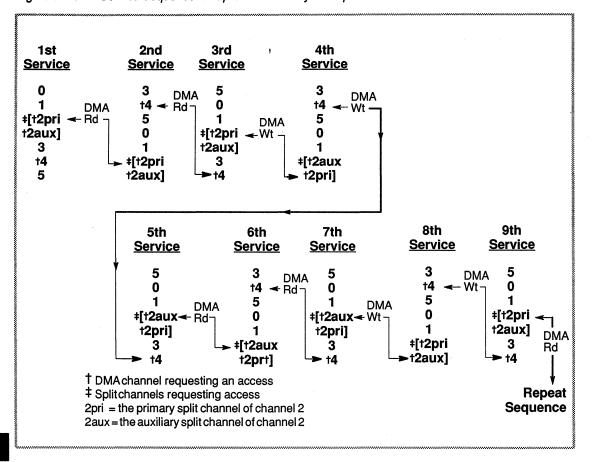

| 9–13             | Service Sequence for Split Mode Priority Example                                                                          | 9-26 |

| 9–14             | Running a DMA Channel Under Transfer Mode 10 <sub>2</sub>                                                                 | 9-29 |

| 9–15             | Running a DMA Channel Under Transfer Mode 11 <sub>2</sub>                                                                 | 9-30 |

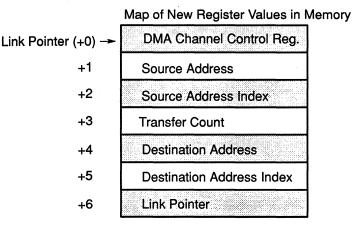

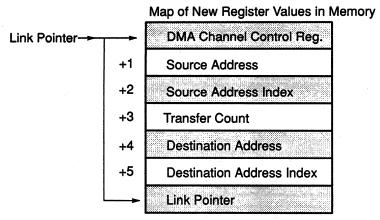

| 9–16             | Store New Values of DMA Channel Registers in Memory (SPLIT MODE = 0)                                                      | 9-32 |

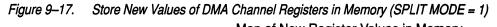

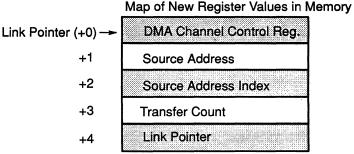

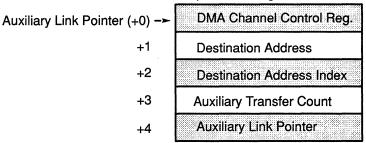

| 9–17             | Store New Values of DMA Channel Registers in Memory (SPLIT MODE = 1)                                                      |      |

| 9–18             | Store New Values of DMA Channel Registers in Memory<br>(SPLIT MODE = 1 and Auxiliary Transfer Counter = 0)                |      |

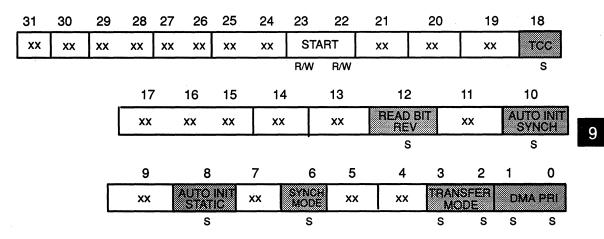

| 9–19             | DMA Channel Control Register Bits That Can Be Modified by<br>Autoinitialization Under Unified Mode                        |      |

| <del>9–</del> 20 | DMA Channel Control Register Bits That Can Be Modified by<br>Autoinitialization of the Primary Channel Under Split Mode   |      |

| 9–21             | DMA Channel Control Register Bits That Can Be Modified by<br>Autoinitialization of the Auxiliary Channel Under Split Mode |      |

| 9–22             | Self-Referential Link Pointer                                                                                             |      |

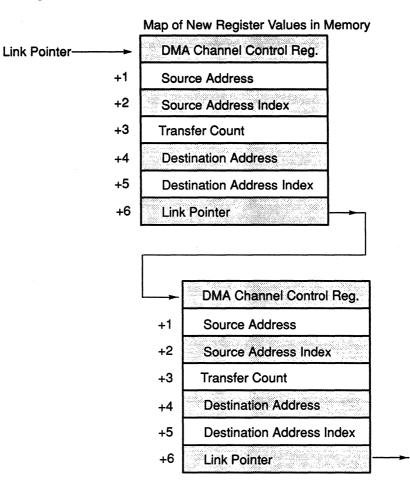

| 9–23             | Referring to a New Link Pointer                                                                                           |      |

| 9-24             | No DMA Synchronization                                                                                                    |      |

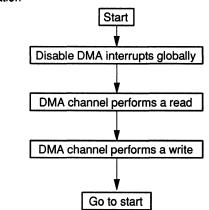

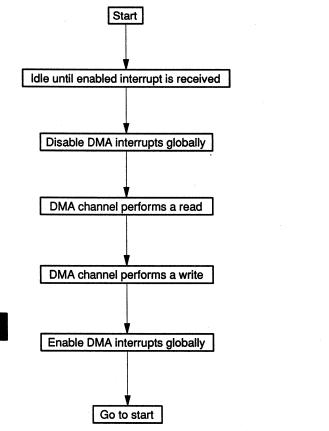

| 925              | DMA Source Synchronization                                                                                                |      |

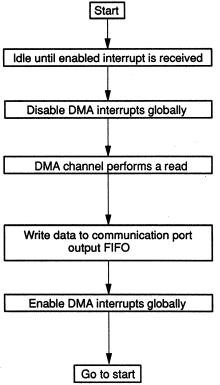

| 9–26             | DMA Destination Synchronization                                                                                           |      |

| 9–27             | DMA Source and Destination Synchronization                                                                                |      |

| 9-28             | Timer Block Diagram                                                                                                       |      |

| 9-29             | Memory-Mapped Timer Locations                                                                                             |      |

| 9–30             | Timer Global-Control Register                                                                                             |      |

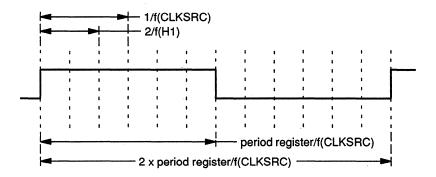

| 9-31             | Timer Timing                                                                                                              |      |

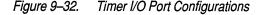

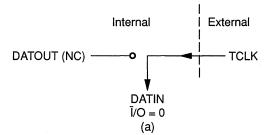

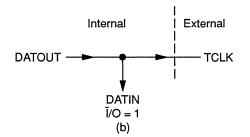

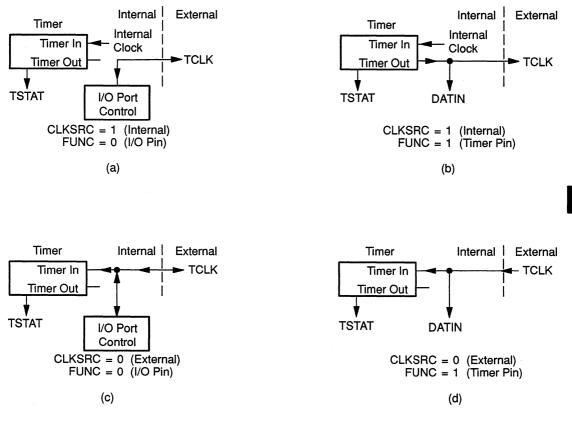

| 9–32  | Timer I/O Port Configurations                                               |

|-------|-----------------------------------------------------------------------------|

| 9–33  | Timer Modes as Defined by CLKSRC and FUNC                                   |

| 10-1  | TMS320C40 Pipeline Structure         10-3                                   |

| 10–2  | Two-Operand Instruction Word 10-21                                          |

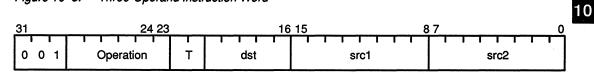

| 10–3  | Three-Operand Instruction Word 10-21                                        |

| 10-4  | Multiply or CPU Operation With a Parallel Store                             |

| 10–5  | Two Parallel Stores 10-23                                                   |

| 10-6  | Parallel Multiplies and Adds 10-24                                          |

| 11-1  | Status Register 11-11                                                       |

| 12–1  | Data Memory Organization for an FIR Filter                                  |

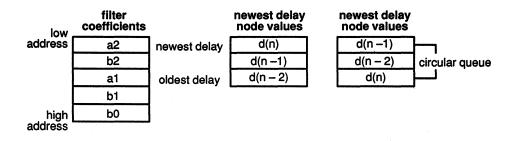

| 12–2  | Data Memory Organization for a Single Biquad 12-54                          |

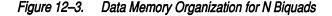

| 12–3  | Data Memory Organization for N Biquads 12-56                                |

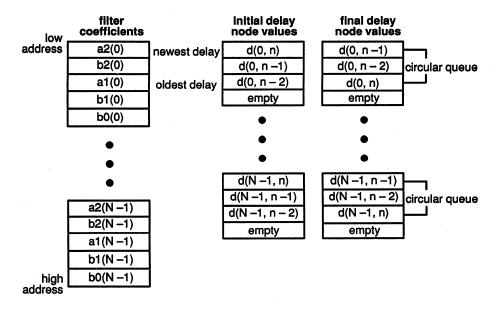

| 12-4  | Data Memory Organization for Matrix-Vector Multiplication 12-61             |

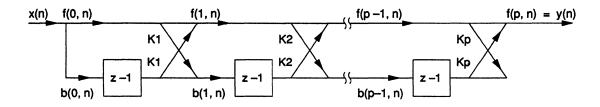

| 12–5  | Structure of the Inverse Lattice Filter 12-89                               |

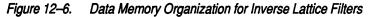

| 12–6  | Data Memory Organization for Inverse Lattice Filters                        |

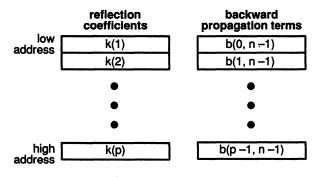

| 12–7  | Structure of the (Forward) Lattice Filter 12-92                             |

| 13–1  | External Interfaces to the TMS320C40 13-3                                   |

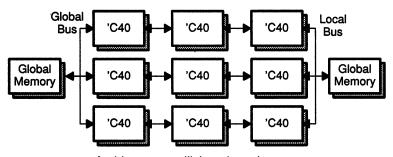

| 13–2  | Possible System Configurations 13-4                                         |

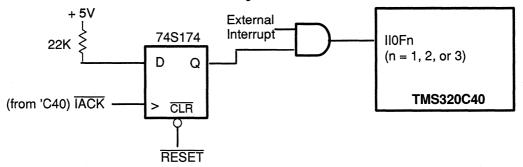

| 13–3  | Circuit for Generation of a Low IIOF Signal for Boot Loader Selection 13-14 |

| 13–4  | Boot Loader Source Program                                                  |

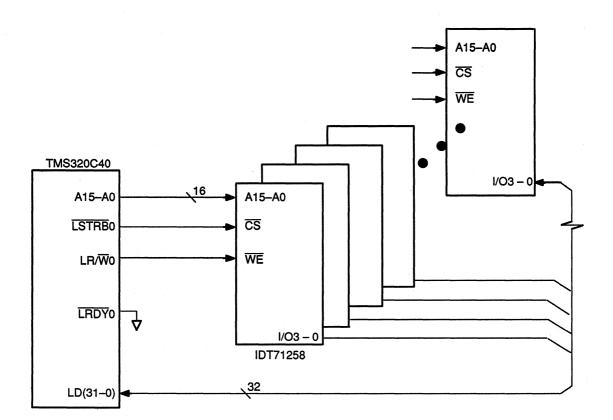

| 13–5  | TMS320C40 Interface to Zero-Wait-State SRAM                                 |

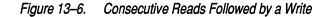

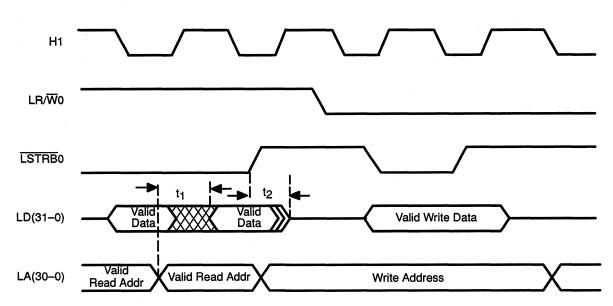

| 13–6  | Consecutive Reads Followed by a Write                                       |

| 13–7  | Consecutive Writes Followed by a Read 13-24                                 |

| 13-8  | TMS320C40 Interface to Zero-Wait-State SRAMs, Two Strobes 13-26             |

| 13–9  | Logic for Generation of 0, 1, or 2 Wait States for Multiple Devices 13-31   |

| 13–10 | State Machine and Equation for the 16R4 PLD                                 |

| 13–11 | Page Switching for the Cypress Semiconductor CY7C185 13-35                  |

| 13-12 | Timing for Read Operations Using Bank Switching                             |

| 13–13 | Message Broadcasting by One 'C40 to Many 'C40s 13-38                        |

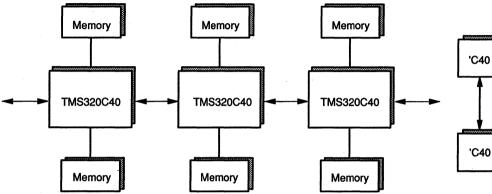

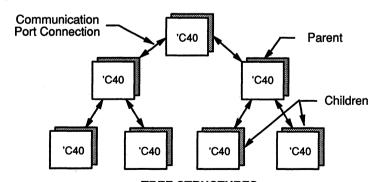

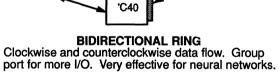

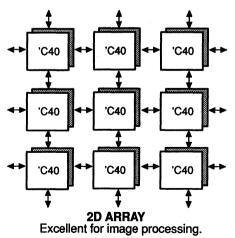

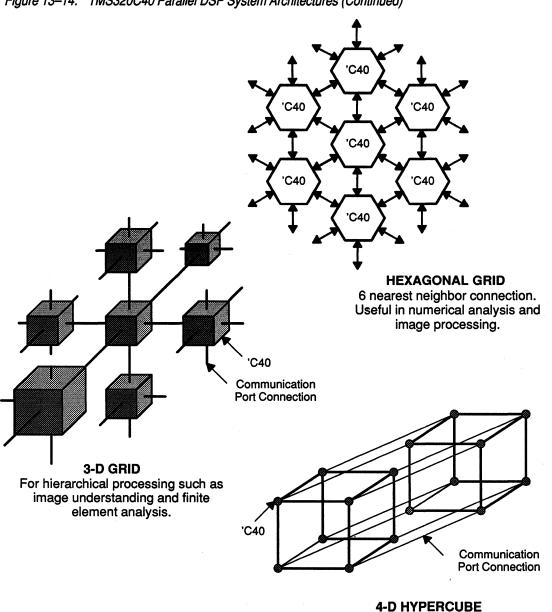

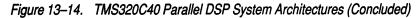

| 13–14 | TMS320C40 Parallel DSP System Architectures                                 |

| 13–15 | TMS320C40 Shared Memory Interface                                           |

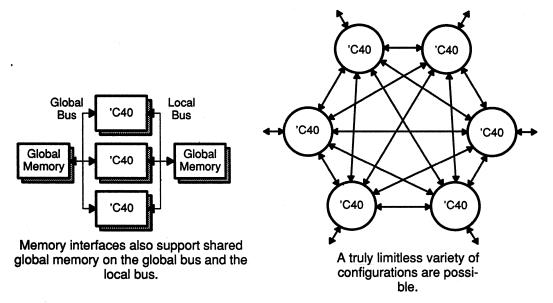

| 13–16 | TMS320C40 Shared Memory and Bus Controller Interface                        |

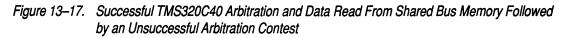

| 13–17 | Successful TMS320C40 Arbitration and Data Read From Shared                  |

|       | Bus Memory Followed by an Unsuccessful Arbitration Contest 13-47            |

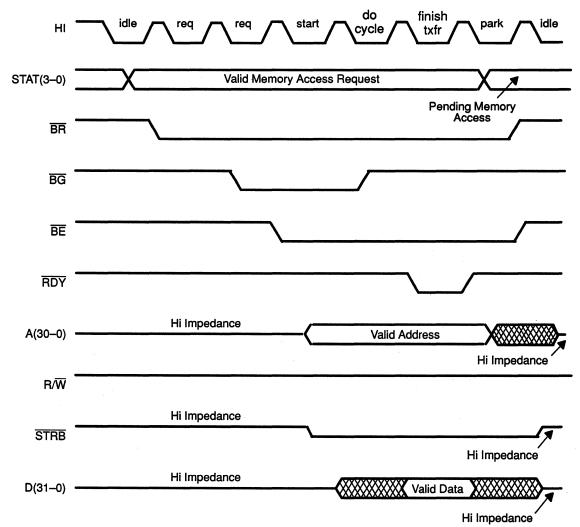

| 13–18 | Shared Bus Interface PLD State Machine                                      |

| 13–19 | PLD Equations for Programming the 16R4 PLD (First-Level Logic) 13-51                                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 13–20 | PLD Equations for Programming the 16R4 PLD 13-60                                                                               |

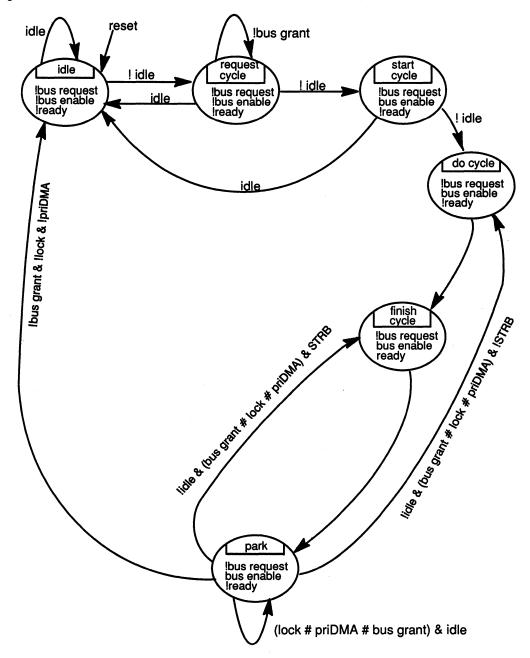

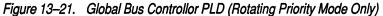

| 13–21 | Global Bus Controllor PLD (Rotating Priority Mode Only) 13-62                                                                  |

| 13–22 | PLD Equations for Programming the 16R8 PLD 13-63                                                                               |

| 13–23 | PLD Equations for Programming the 16R6 PLD 13-68                                                                               |

| 13–24 | Successful TMS320C40 Arbitration; Data Read; Data Read 13-72                                                                   |

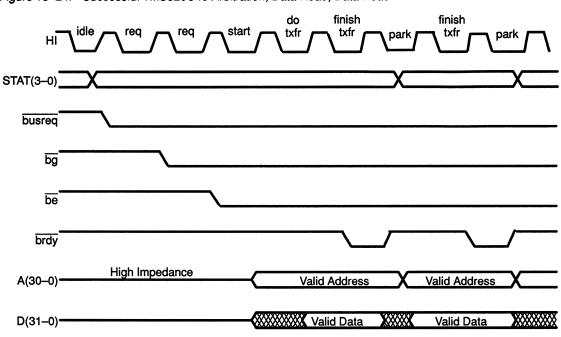

| 13–25 | Successful TMS320C40 Arbitration and Data Write From Shared Bus<br>Memory Followed by an Unsuccessful Arbitration Contest      |

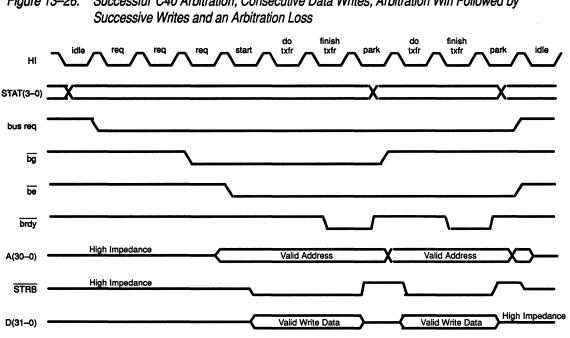

| 13–26 | Successful 'C40 Arbitration; Consecutive Data Writes; Arbitration Win<br>Followed by Successive Writes and an Arbitration Loss |

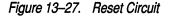

| 13–27 | Reset Circuit                                                                                                                  |

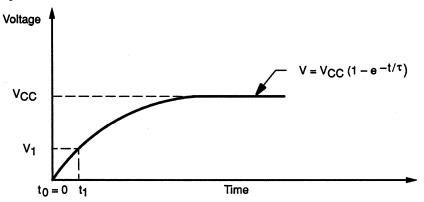

| 13–28 | Voltage on the TMS320C40 RESET Pin                                                                                             |

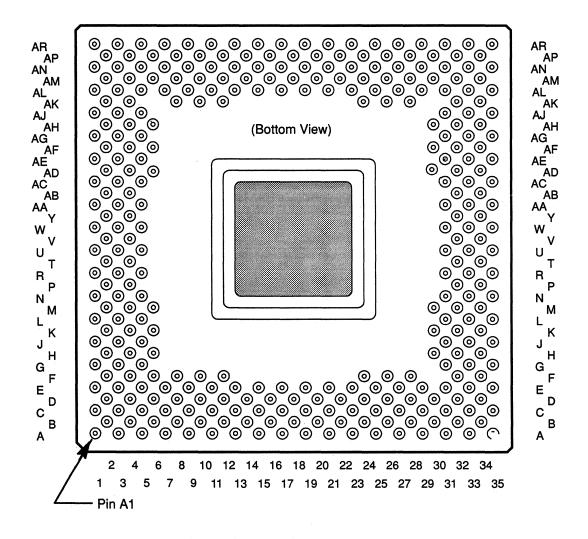

| 14–1  | TMS320C40 Pinout (Bottom View)                                                                                                 |

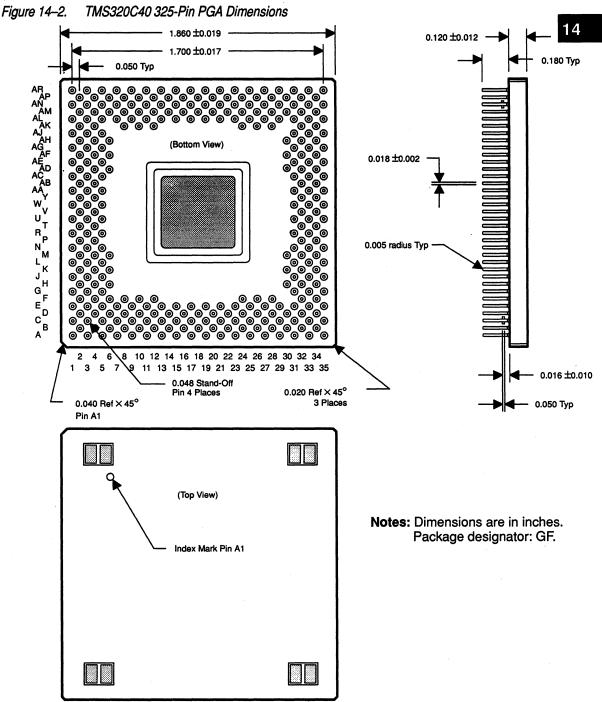

| 14–2  | TMS320C40 325-Pin PGA Dimensions                                                                                               |

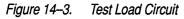

| 14–3  | Test Load Circuit                                                                                                              |

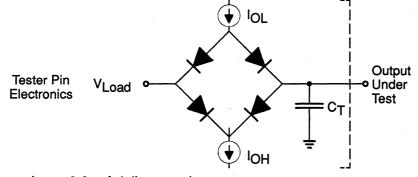

| 14-4  | TTL-Level Outputs 14-14                                                                                                        |

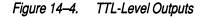

| 14–5  | TTL-Level Inputs 14-14                                                                                                         |

| 14–6  | X2/CLKIN Timing                                                                                                                |

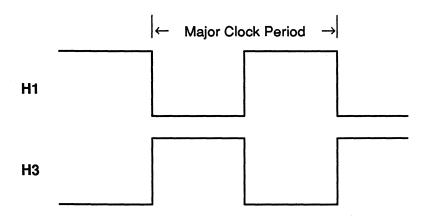

| 14–7  | H1/H3 Timing                                                                                                                   |

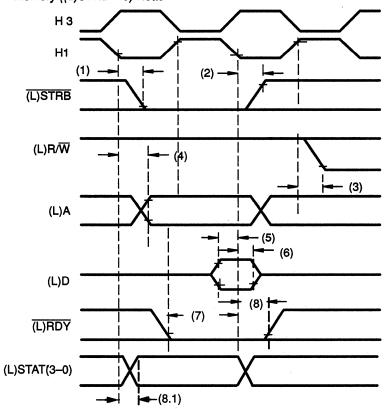

| 14–8  | Memory ((L)STRB = 0) Read                                                                                                      |

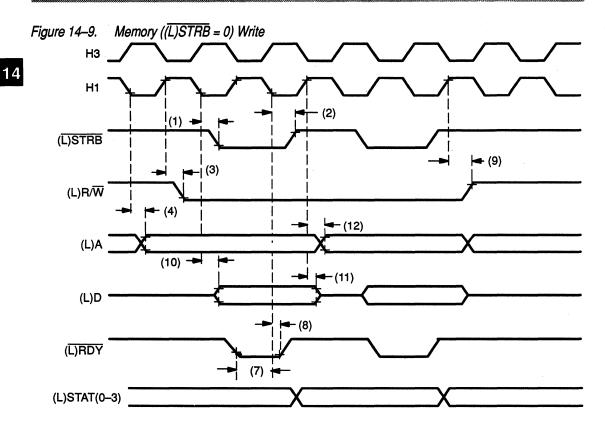

| 14–9  | Memory ((L)STRB = 0) Write                                                                                                     |

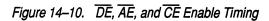

| 14–10 | DE, AE, and CE Enable Timing 14-19                                                                                             |

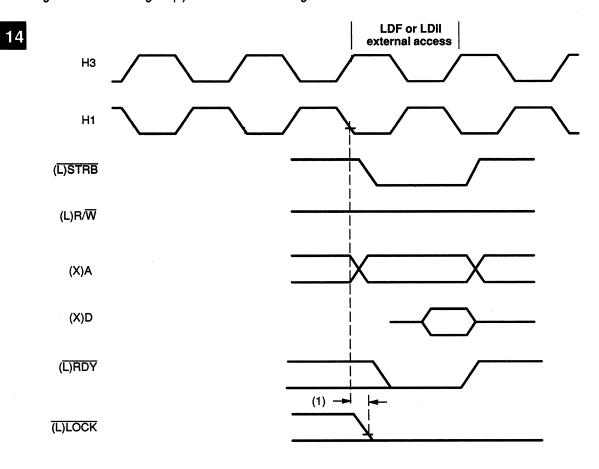

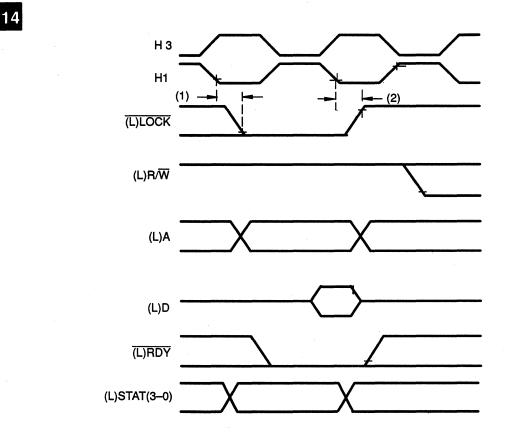

| 14–11 | Timing for (L)LOCK When Executing LDFI or LDII                                                                                 |

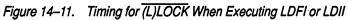

| 14–12 | Timing for (L)LOCK When Executing a STFI or STII                                                                               |

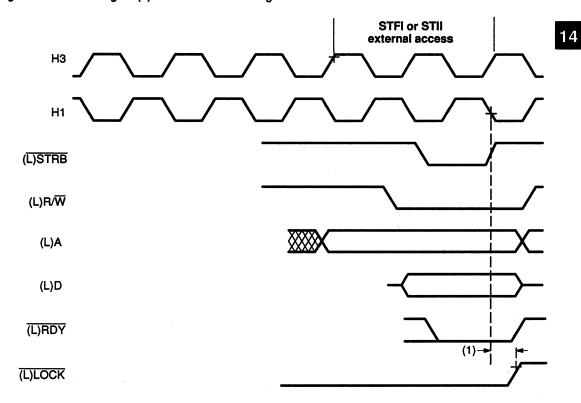

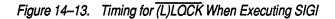

| 14–13 | Timing for (L)LOCK When Executing SIGI                                                                                         |

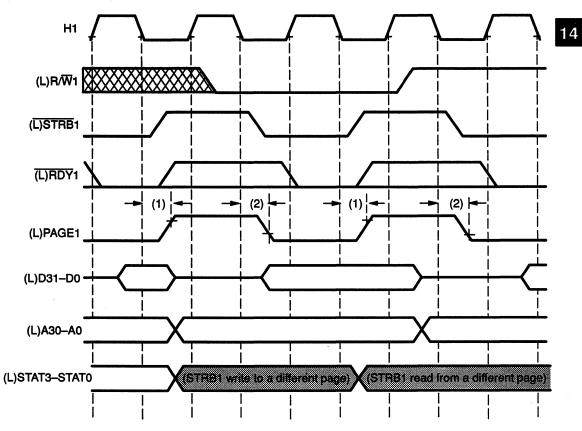

| 14–14 | Timing Parameters for (L)PAGE(0,1) 14-23                                                                                       |

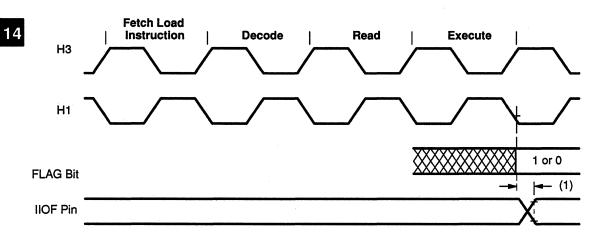

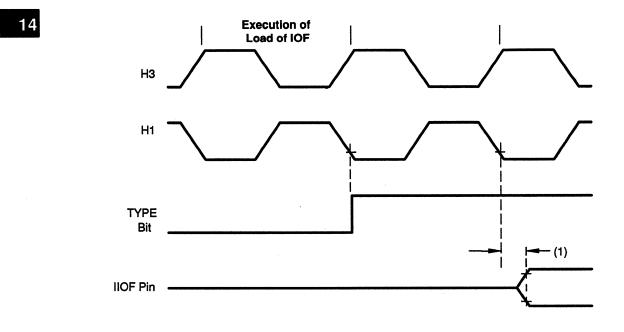

| 14–15 | Timing for Loading IIF Register (IIOF Pins) When Configured as an<br>Output Pin                                                |

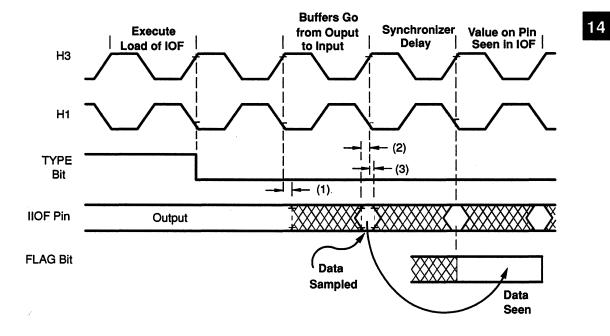

| 14–16 | Change of IIOF From Output to Input Mode                                                                                       |

| 14–17 |                                                                                                                                |

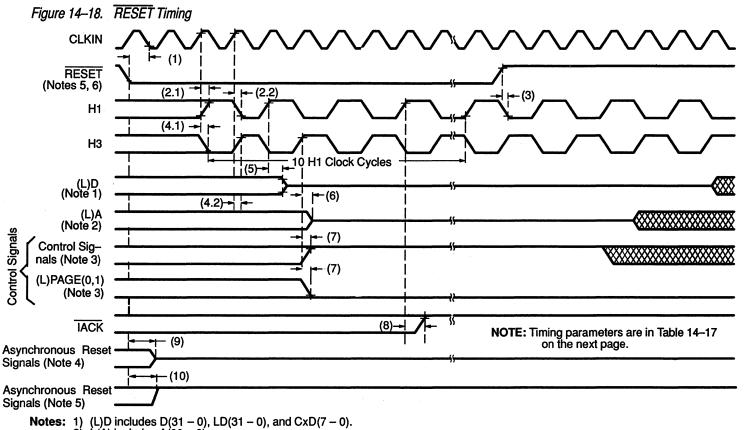

| 14–18 | RESET Timing         14-27                                                                                                     |

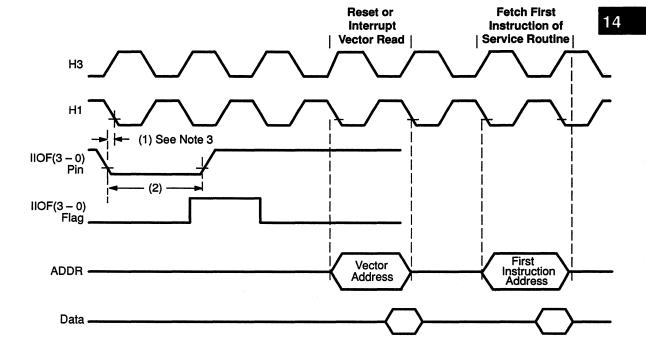

| 14–19 | IOOF(3 — 0) Response Timing                                                                                                    |

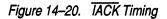

| 14–20 | IACK Timing         14-30                                                                                                      |

| 14–21 | Communication-Port Word-Transfer Cycle Timing                                                                                  |

| 14-22 | Communication Port Byte Timing (Write and Read) 14-32                                                                          |

| 14–23 | Communication Token Transfer Sequence From an Input to an                                                                      |

|       | Output Port 14-33                                                                                                              |

| 14-24 | Communication Token Transfer Sequence From an Output |       |

|-------|------------------------------------------------------|-------|

|       | to an Input Port                                     | 14-35 |

| 14–25 | Timer Pin Timings                                    | 14-37 |

| 14–26 | JTAG Emulation Timings                               | 14-38 |

| A-1   | Tool-Activated ZIF Socket                            | A-2   |

| A-2   | Handle-Activated ZIF Socket                          | A-3   |

| B-1   | 14-pin Header Signals and Header Dimensions          | B-2   |

| B–2   | Emulator Pod Interface                               | B-5   |

| B–3   | Emulator Pod Timings                                 | B-6   |

| B4    | Target-System Generated Test Clock                   | B-7   |

| B–5   | Multiprocessor Connections                           | B-8   |

| B6    | Unbuffered Signals                                   | В-9   |

| B7    | Buffered Signals                                     | В-9   |

## **Tables**

| 2–1 | CPU Primary Registers                                                                          |

|-----|------------------------------------------------------------------------------------------------|

| 2–2 | Instruction Set Summary 2-16                                                                   |

| 2–3 | Parallel Instruction Set Summary 2-23                                                          |

| 3—1 | CPU Primary Register File                                                                      |

| 3–2 | Status Register Bits Summary                                                                   |

| 3–3 | DMA Channels 0 and 1 Synchronization Interrupts (DMA0 and DMA1) 3-9                            |

| 3–4 | DMA Channels 2 to 5 Synchronization Interrupts (DMA2 to DMA5) 3-9                              |

| 3–5 | Summary of Interrupt Enable Register Bits (IIE)                                                |

| 3–6 | IIF Register Bits Summary 3-13                                                                 |

| 3–7 | CPU Expansion Registers 3-15                                                                   |

| 3–8 | Four RESET Vector Locations Chosen by Values on Pins<br>RESETLOC(1,0)                          |

| 3–9 | Combined Effect of the CE and CF Bits                                                          |

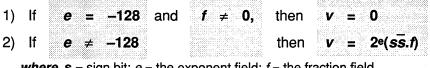

| 4–1 | Rules for Converting IEEE Format to Twos-Complement         Floating-Point Format         4-12 |

| 4–2 | Rules for Converting Twos-Complement Floating-Point Format to IEEE Format                      |

| 5–1 | CPU Register/Assembler Syntax and Function                                                     |

| 5–2 | Indirect Addressing 5-6                                                                        |

| 5–3 | Three-Operand Instruction Address Forms                                                        |

| 5–4 | Index Steps and Bit-Reversed Addressing                                                        |

| 6—1 | Repeat-Mode Registers 6-2                                                                      |

| 6–2 | Interlocked Operations 6-13                                                                    |

| 6–3 | Pin Operation at Reset 6-18                                                                    |

| 7–1 | Global Memory Interface Control Signals                                                        |

| 7–2 | Global Memory Port Status for STRB0 and STRB1 Accesses                                         |

| 7–3 | Bit Definitions for Both Memory Interface Control Registers                                    |

| 7-4 | Page Size as Defined by STRB0/1 PAGESIZE Bits                                                  |

| 7–5   | Address Ranges Specified by STRB ACTIVE Bits                          |

|-------|-----------------------------------------------------------------------|

| 76    | Address Ranges Specified by LSTRB ACTIVE Bits                         |

| 7–7   | Wait-State Generation for Each Value of SWW                           |

| 8–1   | CPCR Bit Functions                                                    |

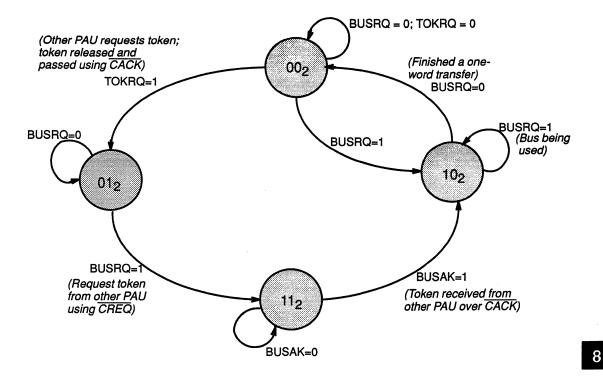

| 8–2   | PAU State Definitions                                                 |

| 8–3   | Summary of Input and Output FIFO Halting                              |

| 8–4   | Handshaking Events in Communication Port Intercommunication 8-20      |

| 8–5   | Communication Port Signals and Synchronizer Delays                    |

| 9–1   | DMA Channel Control Register Bit Definitions                          |

| 9–2   | DMA PRI Bits and CPU/DMA Arbitration Rules                            |

| 93    | TRANSFER MODE and AUX TRANSFER MODE Field Description 9-14            |

| 9–4   | SYNCH MODE Field Description                                          |

| 9–5   | START and AUX START Field Description                                 |

| 9–6   | STATUS and AUX STATUS Field Description                               |

| 9–7   | DMA PRI Bits and CPU/DMA Arbitration Rules                            |

| 9–8   | TRANSFER MODE Field Description Summary                               |

| 9–9   | Effect of SYNC MODE and AUTOINIT MODE Bits in Autoinitialization 9-37 |

| 9–10  | Timer Global-Control Register Bits Summary                            |

| 9—11  | Result of a Write of Specified Values of GO and HLD                   |