# TMS320 DSP Product Overview

The Leader in DSP Solutions

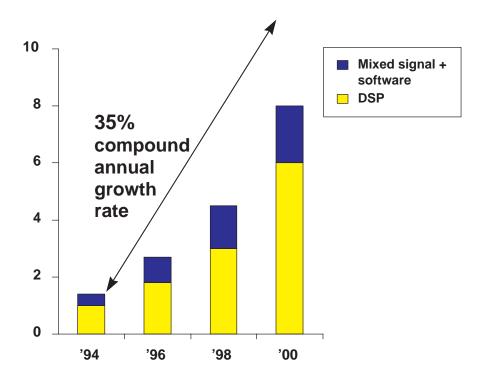

#### **DSP Market**

Texas Instruments (TI) has been the digital signal processor (DSP) market leader since 1982, with the introduction of the TMS32010 DSP. TI continues to be the largest manufacturer of programmable DSPs.

Three factors have driven TI's success:

- Product breadth and DSP solutions

- Development support

- Customizable DSP technology

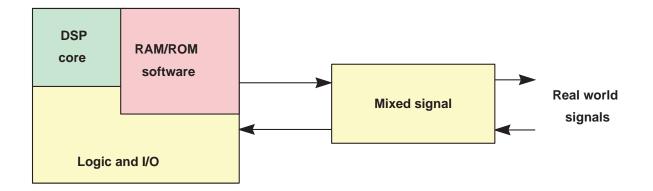

Because of Tl's heavy focus in DSP, Tl has been able to build more products to better fit specific application needs. With more than 100 DSPs to choose from, Tl has the device that gives you the right performance at the right price. Along with this extensive line of DSPs, Tl offers complete system-level DSP solutions, including mixed-signal products and memory, to meet application requirements.

TI continues to help you get your products to market faster because of our broad and innovative development support program. Support is also available from the more than 250 TMS320 third parties.

TI also provides the ability to integrate DSP, logic, and analog and mixed-signal products onto one piece of silicon. When an application requires the ultimate in integration, TMS320 products are the only DSPs that offer a proven migration path to customizable DSPs (cDSP™).

When industry-standard algorithms become solid, TI has the ability to produce application-specific DSPs with maximum cost savings when flexibility is not necessary (e.g., specialized digital compression products).

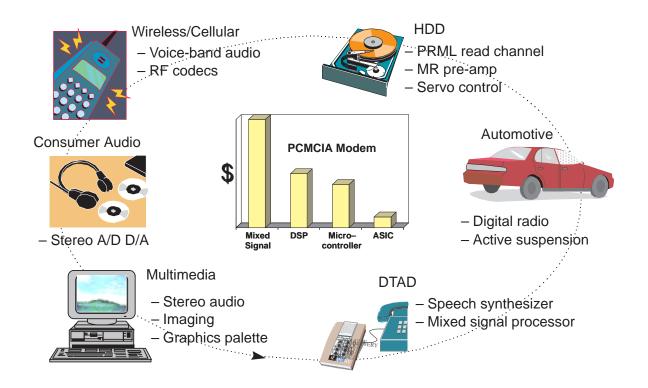

TI continues to gain market share in this expanding market. This growth is fueled by growth in the communication, computer, consumer products, industrial control, instrumentation, military, and office automation arenas. TI is the DSP market share leader.

A fixed-point processor is a processor that does arithmetic operations using integer arithmetic with no exponents. Devices in the TMS320 DSP family which have fixed-point processors are the 'C20x, 'C24x, 'C5x, 'C54x, and 'C62x generations.

A floating-point processor is a processor capable of handling floating-point arithmetic where real operands are represented using exponents. Devices in the TMS320 DSP family that have floating-point processors are the 'C3x, 'C4x, and 'C67x generations.

\*\*cDSP is a trademark of Texas Instruments

# **Exploding Growth in DSP Applications**

# **DSP Solutions Market \$B**

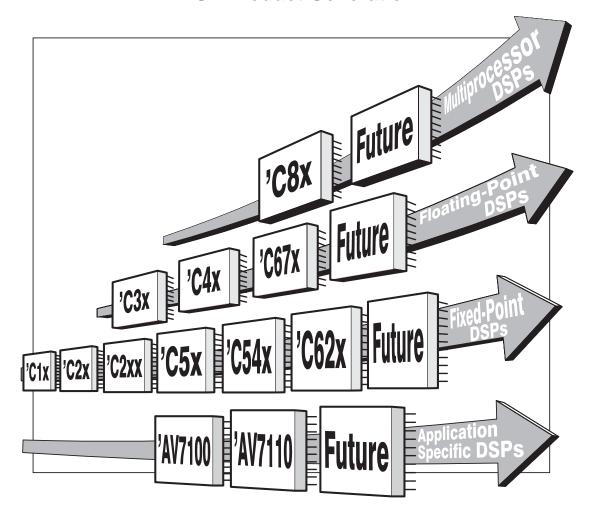

### **DSP Product Generations**

**TMS320C2xx** generation: The TMS320C2xx was introduced in 1995. Manufactured with triple-level metal and full complementary CMOS static logic, the 'C2xx provides 20-40 MIPS performance. The 'C2xx, also available as a core for Tl's customizable DSPs, is the low-cost, fixed-point DSP of the future. The TMS320C24x generation high-speed central processing unit (CPU) allows the use of advanced algorithms, yielding better performance and reducing system component count.

**TMS320C3x** generation: The TMS320C3x is an easy-to-use 32-bit floating-point DSP that achieves 33–60 million floating-point operations per second (MFLOPS) and 16.67–30 MIPS. The architecture of the 'C3x is specifically designed to be an efficient compiler platform. The highly optimized C compiler, the parallel instruction set, and the 'C3x general-purpose features ensure shorter time to market.

**TMS320C4x generation:** The TMS320C4x is a high-performance parallel processor with up to 488 Mbytes/s of data throughput, 40-80 MFLOPS, and 20-40 MIPS. It accepts source code from the 'C3x. Parallel processing development tools are available for the 'C4x.

**TMS320C5x generation:** The TMS320C5x is a high-performance fixed-point DSP that achieves 20-50 MIPS and accepts source code from the 'C1x, 'C2x, and 'C2xx generations. The architecture of the 'C5x generation includes flexible power-management features. The 'C5x is available in low-voltage versions.

**TMS320C54x generation:** The TMS320C54x provides the cost-effective combination of high performance and low power. The 'C54x executes up to 66 MIPS and can operate at 3.0 V, 3.3 V, or 5 V. The specialized architecture is optimized to meet the needs of a variety of existing and emerging worldwide telecommunication and wireless applications.

**TMS320C6x generation:** The TMS320C6x generation offers cost-effective solutions to high-performance DSP programming challenges. The 'C6x devices are the first to feature VelociTI™, which allows performance of up to 1600 million instructions per second (MIPS).

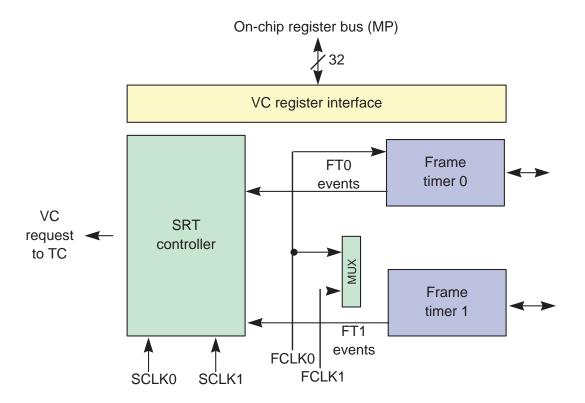

**TMS320C8x** generation: The TMS320C8x integrates multiple (up to four) 32-bit advanced DSPs, a 32-bit RISC master processor with a 100-MFLOPS floating-point unit, a transfer controller with up to 400-Mbytes/s off-chip transfer rate, and up to 50K bytes of on-chip RAM—on a single piece of silicon. The 'C80 also includes two on-chip frame timers.

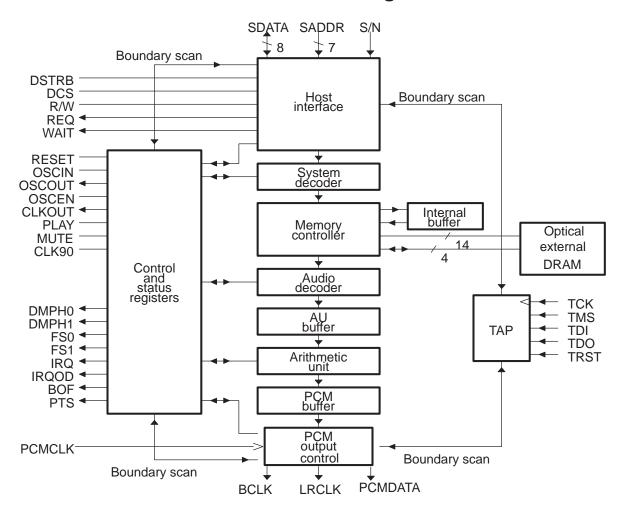

**TMS320AVxxx generation:** The TMS320AVxxx high-speed, application-specific digital compression products meet the demand of compressed audio and video playback in applications such as videoconferencing, digital broadcasting, high-definition TV, graphic workstations, and others supported by international compression standards.

## **DSP Product Generation**

### TMS320C2xx Generation

The combination of advanced Harvard architecture, on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed of the 'C2xx devices.

The 'C2xx generation offers these advantages:

- Enhanced TMS320 architectural design for increased performance and versatility

- Advanced integrated circuit processing technology for increased performance

- Source code compatibility with the 'C1x and 'C2x DSPs

- Upward compatibility with fifth generation DSPs ('C5x)

- New static-design techniques for minimizing power consumption and increasing radiation tolerance

### TMS320C2xx Generation Subfamilies

The 'C2xx generation includes two subfamilies: the general-purpose 'C20x DSPs and the 'C24x DSP controllers that are optimized for digital-control-system type applications.

| TMS320C2xx |      |  |  |  |  |  |

|------------|------|--|--|--|--|--|

| 20x        | 24x  |  |  |  |  |  |

| C203       | F240 |  |  |  |  |  |

| LC203      | C240 |  |  |  |  |  |

| F206       | F241 |  |  |  |  |  |

| C206       | C241 |  |  |  |  |  |

| LC206      | F243 |  |  |  |  |  |

| C209       | C242 |  |  |  |  |  |

### TMS320C20x Features

#### The features for 'C20x are:

- Up to 4.5K data/program RAM on chip

- 32K words of flash memory on chip ('F206 only)

- 32-bit ALU accumulator

- 16 x 16-bit parallel multiplier with a 32-bit product

- Repeat instructions for efficient use of program space and enhanced execution

- 16-bit on-chip timer

- 16-bit barrel shifter

- 8-level hardware stack

- Built-in power-down mode

- Software wait-state generator

- 80- or 100-pin TQFP packages

- Various PLL options for reduced electromagnetic interference (EMI) and system power dissipation

- 'C203, 'LC203, 'C206, 'LC206, and 'F206 are pin-for-pin compatible in a 100-pin TQFP package

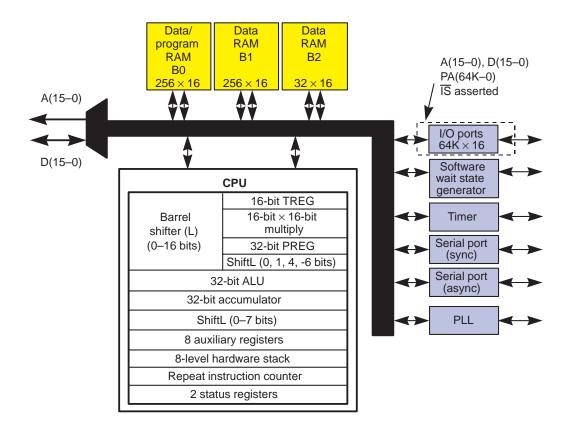

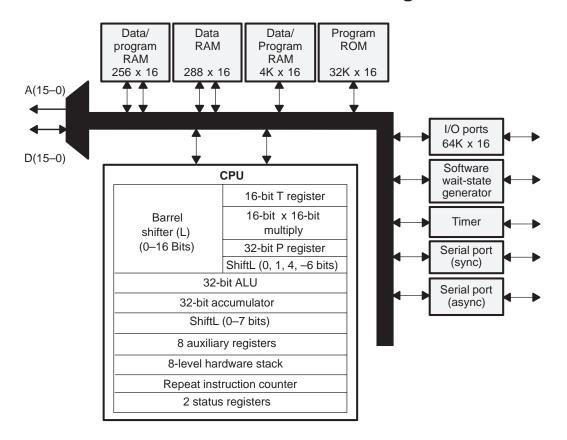

### TMS320C203/LC203

The 'C203 features the core CPU of the 'C2xx generation and several peripherals that optimize it for low-cost, high-volume applications.

The 'C203 has one enhanced synchronous serial port (ESSP) with a 4-level-deep FIFO, which results in less intervention from the CPU, at a low cost. There is also a universal asynchronous receive transmit (UART), a 16-bit timer, and a software wait-state generator. The serial ports, timer, and wait-state generator are each mapped into I/O space.

#### Features of the 'C203 and 'LC203 include:

- 25-, 35-. and 50-ns instruction cycle times ('LC203 50-ns instruction cycle time)

- 3.3-V version, 20 MIPS ('LC203)

- 192K-word external address reach

- 544 words RAM

- Accepts source code from the 'C1x and 'C2x generations

- ANSI C compiler

- ÷2, ×1, ×2, and ×4 PLL options

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex enhanced synchronous serial port (ESSP) with 4-level-deep FIFO

- Full duplex asynchronous serial port

- 100-pin TQFP package

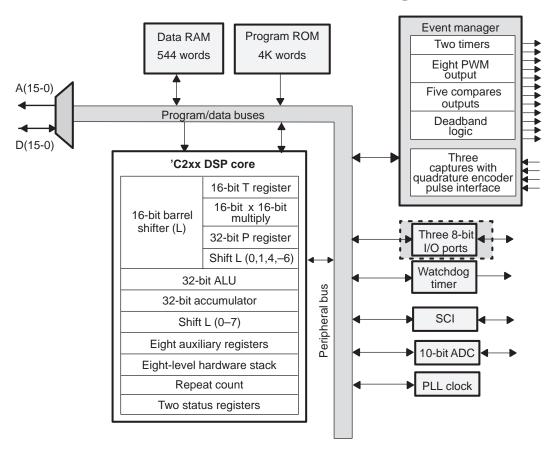

## TMS320C203/LC203 Block Diagram

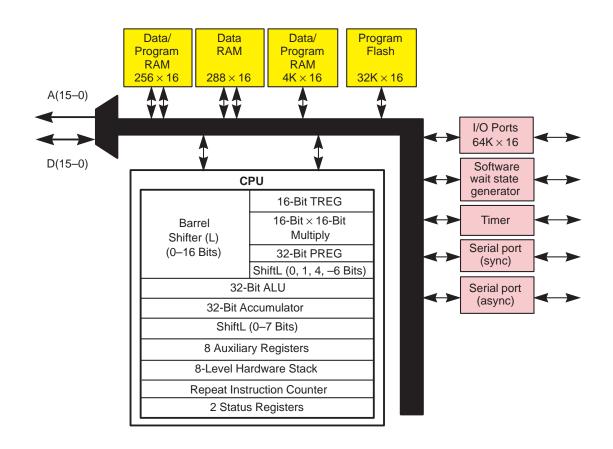

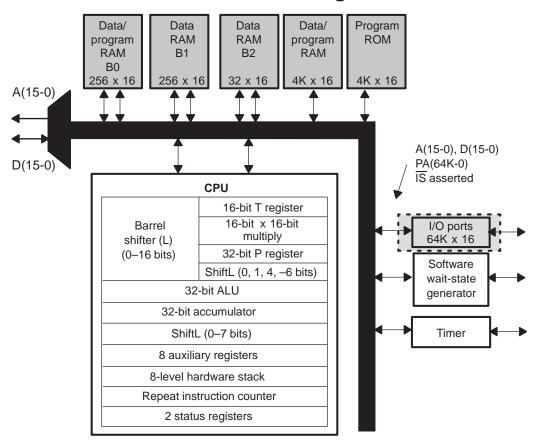

#### TMS320F206

The 'F206 is the first digital signal processor from Texas Instruments with on-chip flash memory. The 'F206 features the core CPU of the 'C2xx generation, several fast, flexible peripherals, and 32K words of flash memory for high-volume, low-cost memory integration. The flash memory can be reprogrammed either by another processor or through an emulator. The 'F206 has the same peripherals as the 'C203 and is pin-for-pin compatible with the 'C203.

#### Features of the 'F206 include:

- 50-ns instruction cycle time

- 192K-word external address reach

- 4.5K words on-chip RAM

- 32K 16-bit words of flash memory

- Accepts source code from the 'C1x and 'C2x generations

- ANSI C compiler

- ÷2, ×1, ×2, and ×4 PLL options

- IEEE 1149.1-standard (JTAG) emulator control

- Full-duplex enhanced synchronous serial port (ESSP) with 4-deep FIFO

- Full duplex asynchronous serial port

- 100-pin TQFP package

- Flash programming utility software

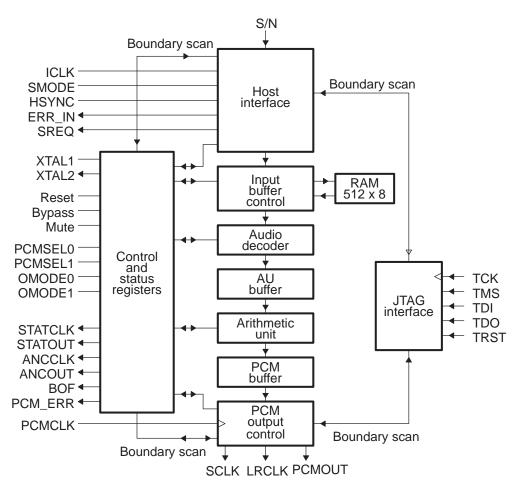

## TMS320F206 Block Diagram

### TMS320C206/LC206

The architecture of the 'C206 is based on that of the TMS320C2xx series and is optimized for low-power operation. The 'C206 is scheduled for sample availability in 2Q '98 and for production in 4Q '98.

#### Features of the 'C206 include:

- 5-V version (3.3-V 'LC206)

- 4.5K-word RAM

- 32K-word ROM

- 192K-word external address reach

- Accepts source code from the 'C1x and 'C2x generations

- ANSI C compiler

- ÷2, x1, x2, and x4 PLL options

- IEEE 1149.1-standard JTAG emulator control

- Full-duplex enhanced synchronous serial port (ESSP) with 4-level deep FIFO

- Full duplex asynchronous serial port

- 100-pin TQFP packaging

- On-chip bootloader

## TMS320C206/LC206 Block Diagram

### TMS320C209

The 'C209 incorporates the 'C2xx core CPU and adds 4K words of RAM and 4K words of ROM on chip. The device has a 16-bit timer and a software wait-state generator; it is packaged in an 80-pin thin quad flat pack (TQFP). The large on-chip memory, small packaging, and low cost make this device attractive for space-constrained applications such as small form factor hard-disk drives.

#### The 'C209 features:

- 35- and 50-ns instruction cycle times

- 4K 16-bit words of RAM

- 4K 16-bit words of ROM

- 192K-word external address reach

- Accepts source code from the 'C1x and 'C2x generations

- ANSI C compiler

- ÷2, ×2 PLL option

- IEEE 1149.1-standard (JTAG) emulator control

- 80-pin TQFP package

## TMS320C209 Block Diagram

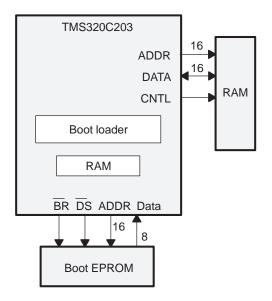

### TMS320C20x Boot Loader

The 'C203 has an on-chip hard-coded boot loader, which allows you to load code from an 8-bit external EPROM into internal or external RAM. The EPROM is mapped into global data memory. Once the boot loading operation begins, 8-bit data is read by the device and reassembled into 16-bit words to a user-specified destination. When complete, control of the device is passed to the start of the program.

#### Features of the 'C20x boot loader are:

- Load from 8-bit external EPROM into internal/external RAM

- EPROM is mapped into global data memory space

- Dedicated boot loader pin

- Backward compatible with 8-bit data in 'C203

- Supports

- 8-bit and 16-bit EPROM

- 8-bit and 16-bit parallel I/O boot

- 8- and 16-bit enhanced synchronous serial ports (ESSPs)

- 8-bit asynchronous serial ports

# TMS320C20x Bootloader Block Diagram

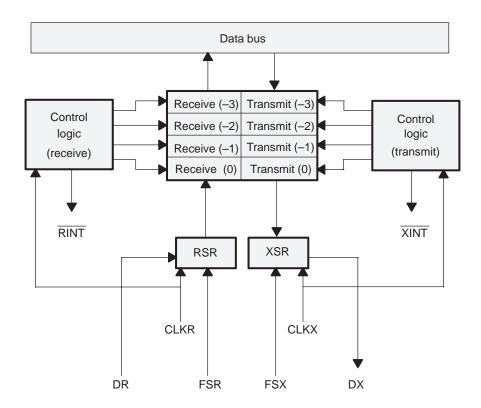

### TMS320C20x Enhanced Synchronous Serial Port (ESSP)

The TMS320C20x offers a full-duplex framed synchronous serial port with up to 20 Mbps throughput (@ 25-ns instruction cycle time). The transfer rate is one-half the device clockout rate. This bidirectional synchronous serial port provides direct communication with serial devices such as codecs, serial ADCs, and other serial systems. The serial port can also be used for intercommunication between processors in multiprocessing applications.

Both the receive and transmit sides of the serial port have a 4-level-deep FIFO buffer which allows the CPU to accept an interrupt at either 1, 2, 3, or 4 levels deep. This capability means less intervention from the CPU, as well as increased flexibility and efficiency with respect to data transfers.

The 'C20x enhanced synchronous serial port (ESSP) features:

- Full-duplex framed synchronous serial port

- Two 4-word × 16-bit buffers to reduce interrupt service routine (ISR) overhead

- Serial port performance

- 20 Mbps at 25 ns

- 14.28 Mbps at 35 ns

- 10 Mbps at 50 ns

- Transfer rate is 1/2 of CPU rate

All 'C2xx devices, except the 'C209, feature this serial port.

# TMS320C20x ESSP Block Diagram

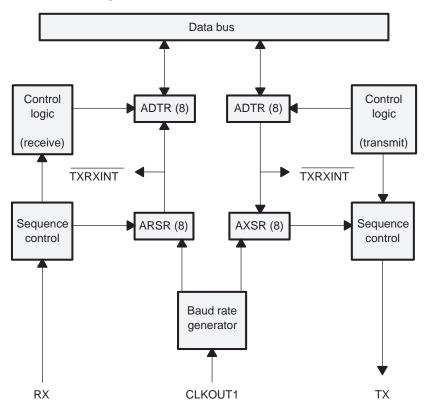

### TMS320C20x Asynchronous Serial Port

The TMS320C20x offers an asynchronous serial port that is full-duplex and double-buffered. It accepts 8-bit data and can be programmed via a register to accept baud rates of up to 2.5 Mbps. The asynchronous serial port can be used to communicate with other devices such as microcontrollers or for RS-232 connections supporting data transfers of up to 250.0 bps.

Features included with the 'C20x asynchronous serial port are:

- Full duplex

- Double buffered

- 8-bit data transfers

- 16-bit register for baud-rate generation

- Baud rates up to 2.5 Mbps (@ 25-ns instruction cycle time)

- Serial-peripheral interface (SPI) module, multi-channel

All 'C2xx devices, except the 'C209, feature this asynchronous serial port.

# TMS320C20x Asynchronous Serial Port Block Diagram

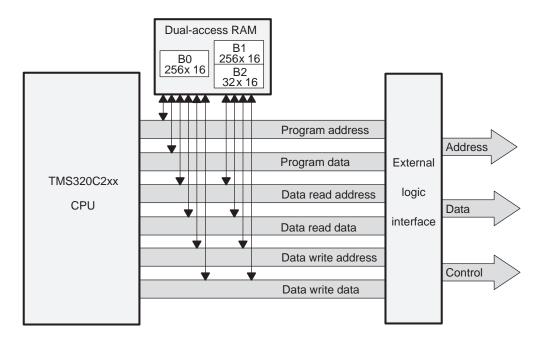

### TMS320C2xx Memory Bus

The 'C2xx advanced Harvard-type architecture maximizes processing power by maintaining two separate memory bus structures, program and data, for full-speed execution. This multiple bus structure allows reading both data and instructions simultaneously. Instructions support data transfers between the two spaces. This architecture lets you store coefficients in program memory to be read in RAM, eliminating the need for a separate coefficient ROM. This, coupled with a 4-level-deep pipeline, allows the TMS320C2xx to execute most instructions in a single cycle.

The 'C2xx dual-access RAM (DARAM) allows writes-to and reads-from the RAM in the same cycle without the address restrictions of SARAM. The dual-access RAM is configured in three blocks: block B0, block B1, and block B2. Block B0 is a 256-word block that can be configured as data or program memory. Block B1 is 256 words in data memory and block B2 is 32 words in data memory.

Some 'C2xx devices also have single-access RAM (SARAM) and/or ROM. Additionally, the 'F206 has flash memory.

The ability of the DARAM to perform two accesses in one cycle, coupled with the parallel nature of the 'C2xx architecture, enables the 'C2xx devices to perform three concurrent memory accesses in any given machine cycle.

# TMS320C2xx Memory Bus Block Diagram

## **TMS320C20x Generation Summary**

All TMS320C20x devices share the same CPU architecture and accept source code from all 'C1x, 'C2x, and 'C2xx devices. This table gives a 'C20x generation product summary so that you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C20x Generation Summary Table**

|             |            | On-Chip Memory<br>(Words) |     | Memory | Serial Ports |      | Vo    |          |      |                   |

|-------------|------------|---------------------------|-----|--------|--------------|------|-------|----------|------|-------------------|

| Product     | MIPS       | RAM                       | ROM | Flash  | Off-Chip     | Sync | Async | Parallel | DMA  | Package<br>(TQFP) |

| TMS320C203  | 20/28.5/40 | 544                       | _   | _      | 64K/64K      | 1    | 1     | 64K x 16 | Ext. | 100               |

| TMS320LC203 | 20         | 544                       | _   | _      | 64K/64K      | 1    | 1     | 64K x 16 | Ext. | 100               |

| TMS320F206  | 20         | 4.5K                      | _   | 32K    | 64K/64K      | 1    | 1     | 64K x 16 | Ext. | 100               |

| TMS320C206  | 40         | 4.5K                      | 32K | _      | 64K/64K      | 1    | 1     | 64K x 16 | Ext. | 100               |

| TMS320LC206 | 40         | 4.5K                      | 32K |        | 64K/64K      | 1    | 1     | 64K x 16 | Ext. | 100               |

| TMS320C209  | 20/28.5    | 4.5K                      | 4K  | _      | 64K/64K      | _    | _     | 64K x 16 | _    | 80                |

### TMS320C24x Features

#### The features for 'C24x are:

- Processing hardware

- 32-bit arithmetic logic unit (CALU)

- 32-bit accumulator

- 16-bit imes 16-bit parallel multiplier with a 32-bit product capability

- Three scaling shifters

- Eight 16-bit auxiliary registers with a dedicated arithmetic unit for indirect addressing of data memory

#### Memory

- 192K words × 16-bit maximum addressable memory space

- On-chip dual-access RAM (DARAM)

- On-chip ROM or flash memory

- External memory interface module with software wait state, 16-bit address lines, and 16-bit data lines

- Support of hardware wait states

- Program control

- Four-level pipeline operation

- Eight-level hardware stack

- User-maskable interrupts

### TMS320C24x Features (continued)

- Instruction set

- Single-instruction repeat operation

- Single-cycle multiply/accumulate instructions

- Memory block move instructions for program/data management

- Indexed-addressing capability

- Bit-reversed indexed-addressing capability for radix-2 FFTs

- Power

- Static CMOS technology

- Four power-down modes to reduce power consumption

- Emulation: IEEE Standard 1149.1 boundary-scan logic interfaced to on-chip scan-based emulation logic

- Speed: 50-ns instruction cycle time, with most instructions single cycle

- Code compatibility with TMS 320 fixed-point devices

- Source code compatible with the 'C25 and 'C2xx devices, and upwardly compatible with the 'C5x generation of DSPs

- On-chip peripherals

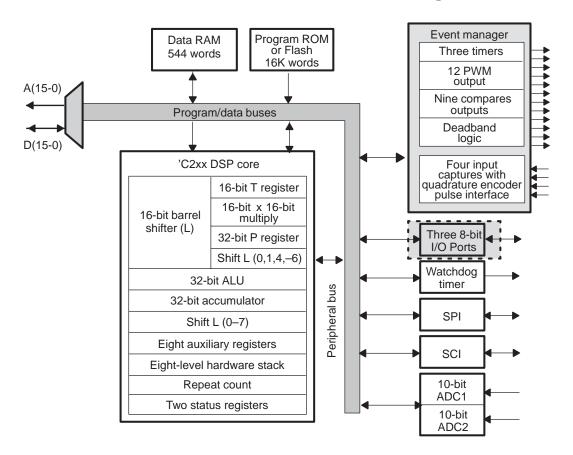

### TMS320C240/F240

These are key features of the 'C240x and 'F240x:

- High-performance static CMOS technology

- Includes the T320C2xLP core CPU

- Source code compatible with TMS320C25;

- Upwardly compatible with TMS320C5x

- 50-ns instruction cycle time

- Memory

- 544K words × 16-bits of on-chip data/program dual-access RAM

- 16K words x x6 bits of on-chip program ROM ('C240) / flash memory ('F240)

- 192K words imes 16 bits of total memory address reach

- Event-manager module (12 PWM outputs)

- Dual 10-bit analog-to-digital conversion module

- 28 individually programmable, multiplexed I/O pins

- Phase-locked loop (PLL)-based clock module

- Watchdog timer module (with real-time interrupt)

- Serial communication interface (SCI) module

- Serial peripheral interface (SPI) module

- Six external interrupts

- Four power-down modes for low-power operation

- Scan-based emulation

- Extended temperature range options available

### TMS320C240/F240 Block Diagram

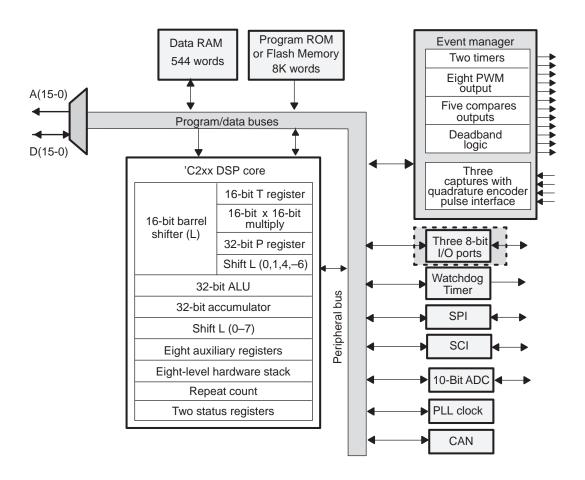

### TMS320C241/F241

The 'C241 device has the following features:

- 'C2xx DSP core, 5-V

- 8K words  $\times$  16 bits of on-chip ROM (Flash memory for 'F241)

- Motor control-optimized event manager (8 PWM outputs)

- 10-bit A/D converter with 800-ns conversion time

- On-chip CAN module (meets specification 2.0B)

- 'C241 supported by the 'F241 for prototyping/preproduction needs

- Extended temperature range options

- 68-pin PLCC, 64-pin PQFP package

- 'F241 footprint-compatible with 'C241 for preproduction prototyping

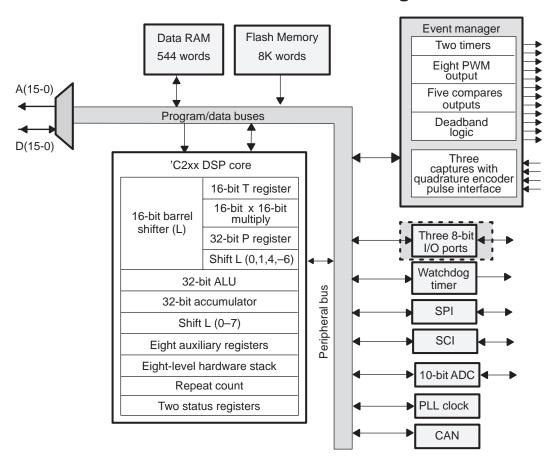

## TMS320C241/F241 Block Diagram

### TMS320C242

The 'C242 device has the following features:

- 'C2xx DSP core, 5-V

- 4K words of on-chip ROM

- Motor control-optimized event manager (8 PWM outputs)

- 10-bit A/D converter with 800-ns conversion time

- Supported by the 'F243 for prototyping/preproduction needs

- No CAN and SPI

- Extended temperature range options

- 68-pin PLCC, 64-pin PQFP package

# TMS320C242 Block Diagram

### TMS320F243

The 'F243 device has the following features:

- 'C2xx DSP core, 5-V

- 8K words of on-chip flash memory

- Motor control-optimized event manager (8 PWM outputs)

- 10-bit A/D converter with 800-ns conversion time

- On-chip CAN module (meets specification 2.0B)

- 16-bit external memory interface

- Extended temperature range options

- 144-pin TQFP package

# TMS320F243 Block Diagram

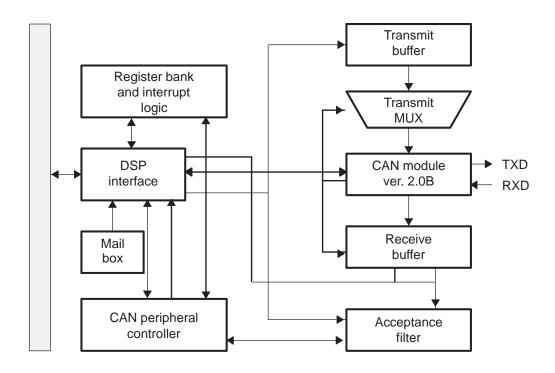

# Controller Area Network (CAN) Module

The 'C241, 'F241, and 'F243 devices include a CAN module. The CAN network uses a serial mutimaster communication protocol that efficiently supports distributed-time control, with a very high level of security and a communication rate of up to one megabit per second ((@ 20-MHz system clock). The CAN bus is ideal for applications operating in a noisy and harsh environment, such as in the automotive or other industrial fields requiring reliable serial communication or multiplexed wiring.

The CAN module provides the CPU with full functionality of the CAN specification, version 2.0B. The module minimizes the CPU's load in communication overhead and enhances the CAN standard by providing additional features.

The following are features of the CAN module:

- Full support for CAN specification 2.0B

- Programmable transmission rate

- Low DSP load for CAN operation and management

- Definition of up to 6 mail boxes

- Selectable interrupt sources

- Internal fault test and confinement

- Automatic transmission timeout

- Low power mode

# **Controller Area Network (CAN) Module**

# **TMS320C24x Generation Summary**

All TMS320C24x devices share the same CPU architecture and accept source code from all 'C1x, 'C2x, and 'C2xx devices. This table gives a 'C24x-generation product summary so that you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C24x Generation Summary Table**

|             |      | On-Chip Memory<br>(Words) |     | Ext.<br>Memory |         |                |     |                       | Timers        |               |               |             |                    |

|-------------|------|---------------------------|-----|----------------|---------|----------------|-----|-----------------------|---------------|---------------|---------------|-------------|--------------------|

| Product     | MIPS | RAM                       | ROM | Flash          | DAT/PRO | A/D            | PWM | Compares/<br>Captures | Gen.<br>Purp. | Watch-<br>dog | Real-<br>Time | I/O<br>Pins | Package            |

| TMS320F240  | 20   | 544                       | -   | 16K            | 64K/64K | Dual<br>10-bit | 12  | 9/4                   | 3             | 1             | 1             | 28          | 132 PQFP           |

| TMS320C240  | 20   | 544                       | 16K | -              | 64K/64K | Dual<br>10-bit | 12  | 9/4                   | 3             | 1             | 1             | 28          | 132 PQFP           |

| TMS320F241  | 20   | 544                       | _   | 8K             | _       | 10-bit         | 8   | 5/3                   | 2             | 1             | -             | 26          | 68 PLCC<br>64 PQFP |

| TMS320F243* | 20   | 544                       | _   | 8K             | 64K/64K | 10-bit         | 8   | 5/3                   | 2             | 1             | _             | 32          | 144 TQFP           |

| TMS320C241  | 20   | 544                       | 8K  | _              | -       | 10-bit         | 8   | 5/3                   | 2             | 1             | _             | 26          | 68 PLCC<br>64 PQFP |

| TMS320C242  | 20   | 544                       | 4K  | -              | _       | 10-bit         | 8   | 5/3                   | 2             | 1             | -             | 26          | 68 PLCC<br>64 PQFP |

<sup>\*</sup> includes external memory interface

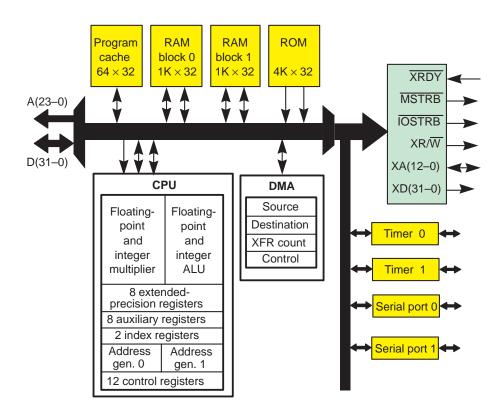

### TMS320C3x Generation

The TMS320C3x generation is the first of TI's 32-bit floating-point digital signal processors. The 'C3x devices provide an easy-to-use, high-performance architecture, that allows users to develop breakthrough products quickly. 'C3x devices can be used in a wide variety of areas including automotive applications, digital audio, industrial automation and control, data communication, and office equipment that include multifunction peripherals, copiers, and laser printers.

The CPU has an independent multiplier and ALU to offer up to 60 million floating-point operations per second (MFLOPS) and up to 30 MIPS.

The direct memory access (DMA) controller has its own data bus and operates in parallel with the CPU. The DMA controller is programmed to input and output data sets, freeing the CPU for arithmetic operations. The DMA controller can reach anywhere in the memory map, including on-chip, off-chip, and memory-mapped peripheral registers.

The total memory space of the 'C3x is 16 million 32-bit words. Having the data, program, and I/O space contained in this 16M-word address range maximizes memory usage and allows you to allocate the memory space as desired.

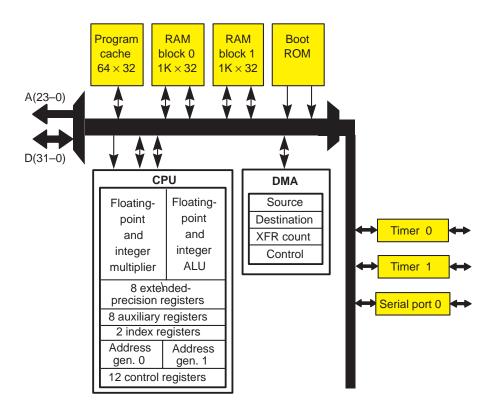

### TMS320C30

The TMS320C30 features two external data buses, two timers, and two serial ports. The primary bus has a 24-bit address bus. The expansion bus has a 13-bit address bus. Both have a 32-bit data bus. Each serial port has independent double-buffered transmit and receive sections with a maximum data rate of 15 Mbps with a 60-MHz input clock.

### Features of the 'C30 include:

- 40-, 50-, and 60-ns instruction cycle times

- 16M-word external address reach

- Single-cycle multiply and accumulate operation

- Two serial ports

- Two timers

- 4K-words on-chip ROM

- Optimizing ANSI C compiler

- On-chip DMA

- 181-pin PGA package

# TMS320C30 Block Diagram

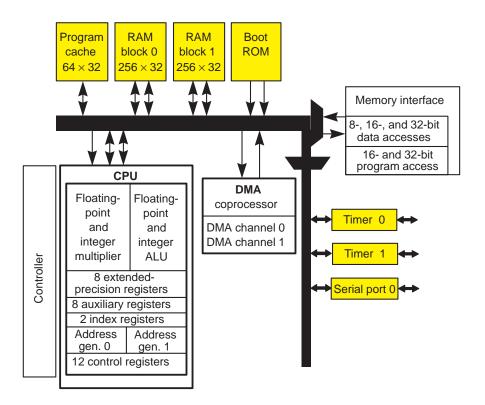

### TMS320C31

The TMS320C31 is the second member of the 'C3x generation and is object-code compatible with the 'C30. The 'C31 has the same fast CPU as all other members of the 'C3x generation but offers a different mix of peripherals to achieve a unique price/performance point.

The 'C31 offers a lower cost than the 'C30 by removing the expansion bus and one of the serial ports, and replacing the 4K 32-bit words of internal ROM with a boot ROM. A low-power version of the 'C31 is available at 40 MHz at 3.3 V that significantly reduces power consumption. The 'C31 comes in a 132-pin plastic quad flat pack (PQFP) package.

#### The 'C31 features:

- 33-, 40-, and 50-ns instruction cycle times

- 16M-word external address reach

- Single-cycle multiply and accumulate operation

- Optimizing ANSI C compiler

- On-chip DMA

- Boot ROM

- 3.3-V version at 40 MHz

- Two low-power modes

- Two 32-bit timers

- Serial port

- 64-word cache

- 132-pin PQFP package

# TMS320C31 Block Diagram

### TMS320C32

The TMS320C32 is the lowest-cost 32-bit floating-point device TI offers. The 'C32 is object-code compatible with the 'C30 and 'C31.

The 'C32 has a flexible memory interface that allows access to 8-, 16-, or 32-bit memory. This can lead to considerable savings in system cost.

There are also two low-power modes on the 'C32. One reduces the clock rate of the device but continues execution, while the other suspends instruction execution and puts the device on hold. These are valuable features in power-critical applications.

The 'C32 features the same boot ROM as the 'C31, has two 256-word  $\times$  32-bit blocks of on-chip RAM, and comes in a 144-pin PQFP package.

#### Features of the 'C32 include:

- 33-, 40-, and 50-ns instruction cycle times

- Object-code compatible with the 'C30 and 'C31

- 16M-word external address reach

- Flexible memory interface (8, 16, or 32 bits)

- Two-channel DMA with configurable priorities

- Low-power modes

- 64-word program cache

- Two 32-bit timers

- 144-pin PQFP package

- Serial port

# TMS320C32 Block Diagram

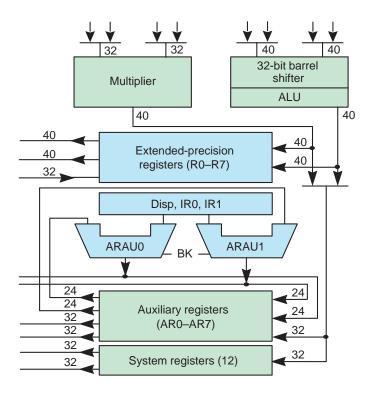

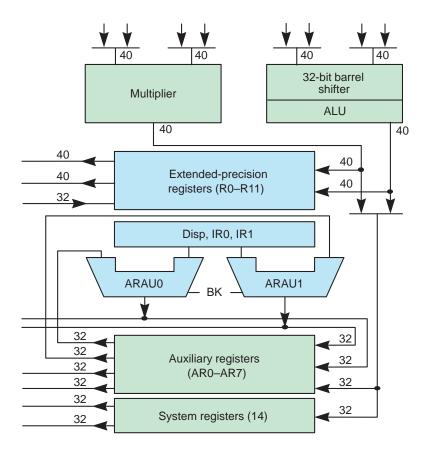

### TMS320C3x CPU

The TMS320C3x CPU has an independent multiplier and accumulator and achieves up to 60 MFLOPS. Results are stored in any one of eight extended-precision registers. These are 40-bit registers that store values with a 32-bit mantissa and an 8-bit exponent. These registers can serve as both the source and destination for any arithmetic operation. The extended-precision registers are an extremely valuable resource for programming in assembly or C. These registers allow you to maintain intermediate results without storing data in memory. This results in higher-performance assembly code and a more efficient C compiler.

To sustain 60 MFLOPS, the CPU has two independent auxiliary register arithmetic units (ARAUs). The two ARAUs generate 24-bit addresses that are accessed via the eight auxiliary registers. The ARAUs can perform any of these functions:

- Pre or postincrement or decrement

- Index offset for increment and decrement values other than 1

- Circular addressing to support circular buffers

- Bit-reversed addressing for FFTs

#### Features of the 'C3x CPU include:

- 60-MFLOP CPU

- Register-based CPU

- 32 or 40 floating-point/integer multiplier

- 32 or 40 floating-point/integer ALU

- 32-bit barrel shifter

- Eight 40-bit extended-precision registers

- Two address generators

- Two index registers

- Eight indirect-address registers

# TMS320C3x CPU Block Diagram

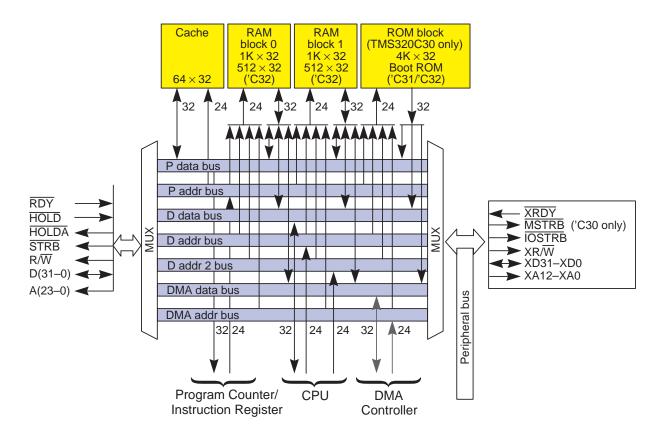

### TMS320C3x Memory

To realize the full performance of the 'C3x CPU, it is important to have a bus and memory architecture that can keep pace. The 'C3x fetches up to four words each cycle. These consist of a program opcode, two CPU data operands, and a DMA data transfer. The internal buses can transfer all four words in parallel, relying on seven memory sources for data.

The 'C3x uses seven internal buses to access on-chip resources:

- Program address/data: The CPU uses these buses to maintain instruction fetches every cycle.

- Data address/data: In any cycle, the CPU can fetch two data operands, because it has two data address buses

and one data bus that can be accessed twice in a single cycle.

- DMA address/data: The DMA uses these buses to perform DMA transfers in parallel with CPU operation.

With the internal buses in place to feed the DMA and CPU, the 'C3x devices can use both internal and external data and program memory. The 'C30 and 'C31 have two 1K 32-bit word blocks of dual-access RAM, while the 'C32 has two 256 32-bit word on-chip RAMs. This memory provides up to four words of program or data in a single cycle. All 'C3x devices feature an on-chip cache to boost system performance. The primary bus for each device has 16M words of address reach. The 'C30 features an expansion bus that has an 8K-word address reach, which is often used to interface to peripherals.

The 'C32 offers the ability to access 8-/16-/32-bit data stored in 8-/16-/32-bit wide external memory giving the flexibility of nine memory interface options. This feature can significantly affect total system cost savings. Additionally, the 'C32 memory interface allows for storage of the 32-bit instruction word in either 16- or 32-bit-wide external memory.

# TMS320C3x Memory Block Diagram

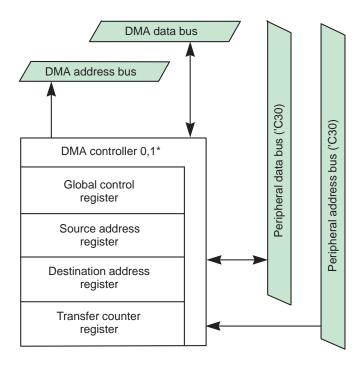

### TMS320C3x DMA Controller

The DMA controller transfers data between memory resources. The serial ports and timers on the 'C3x are memory-mapped, allowing DMA transfers to and from these peripherals. To perform a transfer, the DMA reads a memory location pointed to by the source address register and then writes to the memory location pointed to by the destination address register. The source and destination addresses are incremented or decremented after each transfer, depending on the value of the global control register. The DMA controller performs continuous transfers over the DMA bus until the value in the transfer counter register reaches 0, and a programmable interrupt is sent to the CPU.

For example, an application might use the DMA to transfer 512 words from slow external memory to the on-chip RAM. At the completion of the transfer, an interrupt is sent to the CPU to process and output results while the DMA transfers a new set of 512 words to on-chip RAM. By off-loading data input, the DMA controller allows sustained CPU performance for arithmetic calculations. In this case, the CPU always has zero-wait-state access to data, even though the external memory requires one or more wait states.

The 'C32 offers the programmer the flexibility of designating priority on the bus. There are three options:

- The CPU has priority over the DMA at all times ('C30 and 'C31)

- The DMA controller has priority over the CPU

- The CPU and DMA share a rotating priority with the CPU having first access

### Features of the DMA controller include:

- Increased CPU-sustained performance by virtually eliminating CPU I/O

- Memory-to-memory transfers

- 2-channel configurable priority ('C32 only)

- Programmable increment or decrement of addresses

# TMS320C3x DMA Controller Block Diagram

<sup>\*</sup> DMA1 is available only on the 'C32.

### TMS320C3x Sum of Products Example

The following code for a sum of products is typical of DSP algorithms and demonstrates the power of the 'C3x architecture. First, note that the repeat single instruction (RPTS) is used for a zero-overhead loop. The parallel bars next to the ADDF instruction indicate that the addition is executed in parallel with the multiplication. Auxiliary registers 0 and 1 are used to fetch the two data operands with a post-increment of one. The multiplier results are placed in one of the eight extended-precision registers. The extended-precision register set is further used as the input and output for the addition. Finally, the DMA can transfer the next set of data for the CPU to process in parallel with the multiply and accumulate. All of these operations take place in a single cycle, illustrating the parallelism in the 'C3x architecture.

# TMS320C3x Sum of Products Example

# **TMS320C3x Generation Summary**

All TMS320C3x devices share the same CPU architecture and accept source code from all 'C1x, 'C2x, and 'C2xx devices.

This table gives a 'C3x-generation product summary so that you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C3x Generation Summary Table**

|              |                |                       | Memory         | On Chip        |                    | Peripherals           |        |     |              |

|--------------|----------------|-----------------------|----------------|----------------|--------------------|-----------------------|--------|-----|--------------|

| Data<br>Type | Device         | Cycle<br>Time<br>(ns) | RAM<br>(Words) | ROM<br>(Words) | Memory<br>Off Chip | On-<br>Chip<br>Timers | Serial | DMA | Package      |

| 32-Bit       | TMS320C30†     | 60                    | 2K             | 4K             | 16M × 32           | 2                     | 2      | 1   | 181-pin PGA  |

| Floating-    | TMS320C30-40†  | 50                    | 2K             | 4K             | 16M × 32           | 2                     | 2      | 1   | 181-pin PGA  |

| point        | TMS320C30-50   | 40                    | 2K             | 4K             | 16M × 32           | 2                     | 2      | 1   | 181-pin PGA  |

| word         | TMS320C31-40†‡ | 50                    | 2K             | Boot           | 16M × 32           | 2                     | 1      | 1   | 132-pin PQFP |

|              | TMS320LC31-40  | 50                    | 2K             | Boot           | 16M × 32           | 2                     | 1      | 1   | 132-pin PQFP |

|              | TMS320C31-50†‡ | 40                    | 2K             | Boot           | 16M × 32           | 2                     | 1      | 1   | 132-pin PQFP |

|              | TMS320C31-60   | 33                    | 2K             | Boot           | 16M × 32           | 2                     | 1      | 1   | 132-pin PQFP |

|              | TMS320C32-40‡  | 50                    | 512            | Boot           | 16M × 8/16/32      | 2                     | 1      | 2   | 144-pin PQFP |

|              | TMS320C32-50†‡ | 40                    | 512            | Boot           | 16M × 8/16/32      | 2                     | 1      | 2   | 144-pin PQFP |

|              | TMS320C32-60   | 33                    | 512            | Boot           | 16M × 8/16/32      | 2                     | 1      | 2   | 144-pin PQFP |

<sup>†</sup> Military version available ‡ Extended temperature version is available

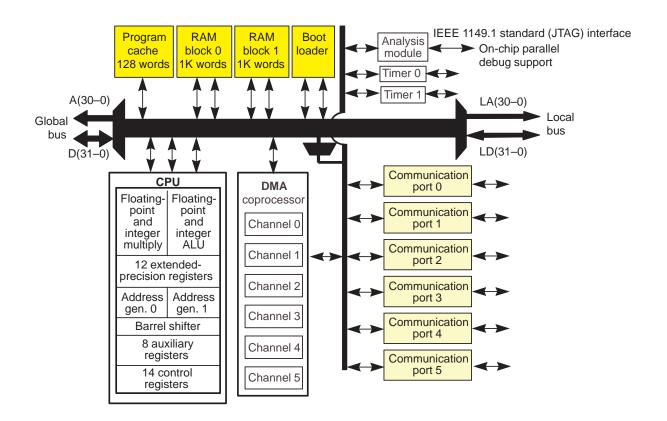

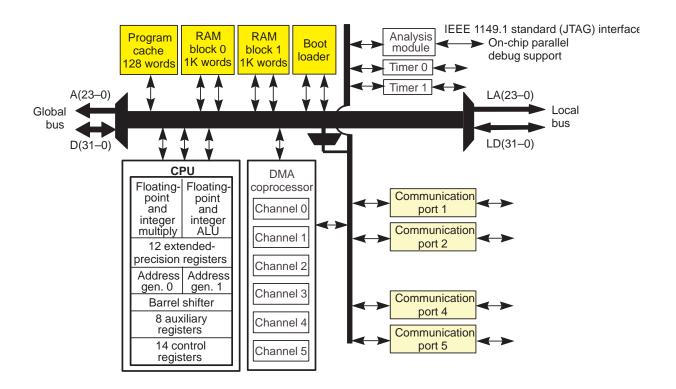

### TMS320C4x Generation

The TMS320C4x devices are 32-bit floating-point digital signal processors optimized for parallel processing. The 'C4x family combines a high-performance CPU and DMA controller with up to six communication ports to meet the needs of multiprocessor and I/O-intensive applications. All 'C4x devices are compatible with TI's multichip development environment. Each device contains an on-chip analysis module that supports hardware breakpoints for parallel-processing development and debugging. The 'C4x family accepts source code from the TMS320C3x family of floating-point DSPs. Key applications of the 'C4x family include 3-dimensional graphics, image processing, networking, and telecommunications base stations.

### TMS320C40

The TMS320C40 is the original member of the 'C4x family. It features a CPU that can deliver up to 30 MIPS/60 MFLOPS with a maximum I/O bandwidth of 384 Mbytes/s. The 'C40 has 2K words of on-chip RAM, 128 words of program cache, and a boot loader. Two external buses provide an address reach of four gigawords of unified memory space. The 'C40 is available in a 325-pin CPGA package.

### Features of the 'C40 include:

- 33-/40-ns instruction cycle times for the 'C40

- 4G-word external address reach

- Accepts source code from the 'C3x

- Optimizing ANSI C compiler

- IEEE floating-point conversion for ease of use

- 6- or 12-channel on-chip DMA

- Six communication ports

- 325-pin PGA package

### TMS320C40 Block Diagram

### TMS320C44

The TMS320C44 is a lower-cost version of the 'C40 for parallel-processing applications that are more price sensitive. The 'C44 features four communications ports and has an external address reach of 32M words over two external buses. To further reduce cost, the 'C44 comes in a 304-pin PQFP package or a 388-pin BGA. The 'C44 can deliver up to 30 MIPS/60 MFLOPS performance with a maximum I/O bandwidth of 336 Mbytes/s. The 'C44 source code can be used with the 'C40.

#### Features of the 'C44 include:

- 33- and 40-ns instruction cycle times

- Idle mode for reduced power consumption

- Four communication ports

- 32M-word external address reach

- 6- or 12-channel on-chip DMA

- Optimizing ANSI C compiler

- IEEE floating-point conversion for ease of use

- The 'C44 source code can be used with the 'C40

- 304-pin PQFP package

- 388-pin BGA

## TMS320C44 Block Diagram

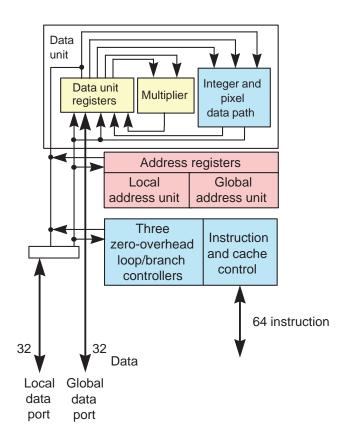

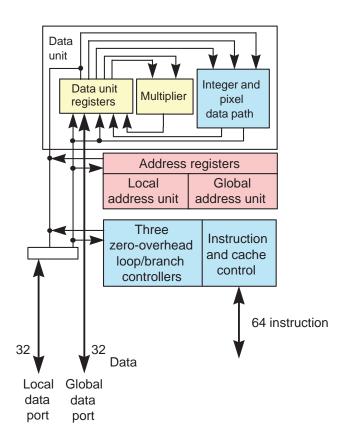

### TMS320C4x CPU

The TMS320C4x has an independent multiplier and accumulator, and achieves up to 60 MFLOPS. Results are stored in any one of 12 extended-precision registers. These are 40-bit registers that store values with a 32-bit mantissa and an 8-bit exponent. These registers can serve as both the source and the destination for any arithmetic operation. The extended-precision registers are an extremely valuable resource for programming in assembly or C. These registers allow you to maintain intermediate results without storing data in memory. This results in higher performance assembly code and a more efficient C compiler.

To sustain 60 MFLOPS, the CPU has two independent auxiliary register arithmetic units (ARAUs), which can generate two addresses in a single cycle. The two ARAUs operate in parallel with the multiplier and ALU. They support addressing with displacements, addressing with index registers (IR0 and IR1), circular addressing, and bit-reversed addressing.

#### Features of the 'C4x CPU are:

- High-speed internal parallelism: eight operations/cycle for maximum sustained performance

- Floating-point/integer multiply

- Floating-point/integer addition

- Two data accesses

- Zero-overhead branch and loop counter update

- IEEE floating-point conversion

- Divide and square root support for improved performance

- Single-cycle byte and halfword manipulation capabilities

- Register-based CPU

# TMS320C4x CPU Block Diagram

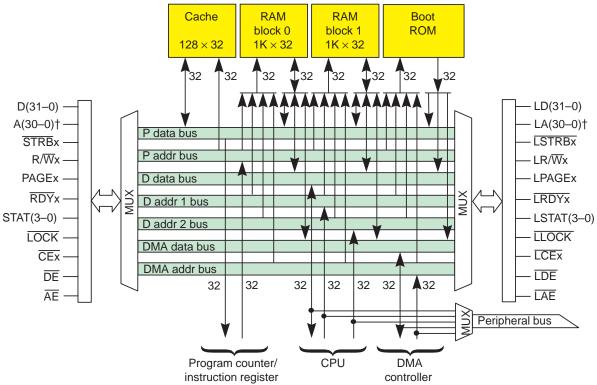

## TMS320C4x Memory and Bus Structure

To realize the full performance of the 'C4x CPU, it is important to have a bus and memory architecture that can keep pace. The 'C4x fetches up to four 32-bit words each cycle: a program opcode, two CPU data operands, and a DMA data transfer. The internal buses can transfer all four words in parallel, relying on seven memory sources for data.

The 'C4x uses seven internal buses to access on-chip resources:

Program address/data: The CPU uses these buses to maintain instruction fetches every cycle.

**Data address/data:** In any cycle, the CPU can fetch two data operands because it has two data address buses and one data bus that can be accessed twice in a single cycle.

**DMA** address/data: The DMA uses these buses to perform DMA transfers in parallel with CPU operation.

With the internal buses in place to feed the DMA and CPU, the 'C4x-generation devices can use both internal and external data and program memory. Internally, the 'C4x has two  $1K \times 32$ -bit word blocks of dual-access RAM, providing up to four words of program or data in a single cycle. For external memory, the 'C40 has two identical 32-bit buses, which address up to 2G words of memory each. The 'C44 has two 24-bit external address buses, which address up to 16M words each. Each device has an on-chip instruction cache to boost performance when using slower external memory.

# TMS320C4x Memory and Bus Structure Block Diagram

† 24-bit address bus in TMS320C44

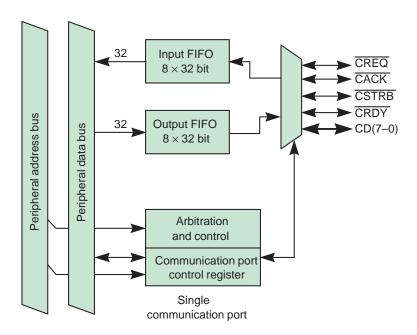

### TMS320C4x Communication Ports

The communication ports on the 'C4x generation transfer up to 24 Mbytes/s each for asynchronous interprocessor communications or for servicing intensive I/O needs. The 'C40 has six ports, and the 'C44 has four. Each port has four control pins and eight data pins. These 12 pins provide a glueless interface to another 'C4x. The control pins, combined with the control logic, arbitrate with another device to determine data transfer timing and direction. Because the communication ports have built-in arbitration and control circuitry, you simply need to read data from and write data to the memory-mapped input and output FIFOs.

In a typical transfer, the DMA coprocessor or the CPU first writes to the output FIFO. Next, the communication port sends a request signal to the destination processor, which responds with an acknowledge. The communication port then transfers the word as four successive bytes. The destination processor receives the word in its input FIFO, where the destination DMA or CPU can read the contents. Note that the input and output FIFOs provide a 16-word  $\times$  32-bit buffer between communications ports.

Features of the 'C4x communication ports include:

- Up to 24 Mbytes/s bidirectional interface on each communication port for high-speed and low-cost parallel-processor interface

- 8-word deep input FIFO and 8-word deep output FIFO buffer

- Automatic arbitration and handshaking for direct processor-to-processor connection

# TMS320C4x Communication Ports Block Diagram

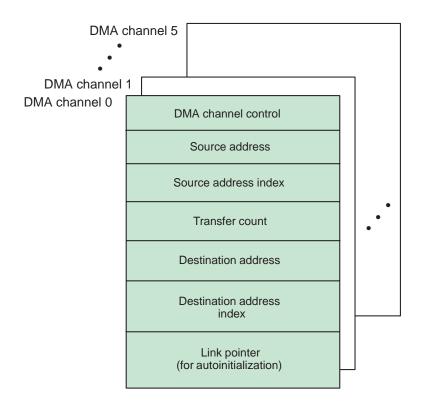

### TMS320C4x DMA Coprocessor

With as many as six communication ports and two external buses, the TMS320C4x has an I/O capability of as much as 384 Mbytes. To service this speed, the 'C4x has a 6- or 12-channel DMA which operates independently of the CPU and has dedicated address and data buses to avoid bus conflicts.

The DMA is programmed to transfer data from one memory location to another (communication ports are memory-mapped). The DMA can begin a task based on CPU or external interrupts and can interrupt the CPU at the completion of a task. The DMA also includes a link pointer register that allows the DMA to program its next task without CPU intervention.

Since each communication port has transmit and receive capability, 12 DMA channels are needed if all six communication ports are being used in a bidirectional mode. The DMA has a split-mode operation dedicated to this function, allowing it to service the 12 input and output FIFOs in the communication ports.

In the event that both the CPU and DMA are accessing the same resource, priorities can be assigned to the CPU, the DMA, or mixed, where the CPU gets the first access followed by the DMA, to resolve the conflict.

The 'C4x DMA coprocessor features:

- Concurrent I/O to maximize sustained CPU performance

- Autoinitialization

- Up to 6 or 12 DMA channels for parallel data transfers

- Data transfers to and from anywhere in memory

- Three operations/cycle

- 32-bit data transfer

- Address register update

- Transfer counter update

- Performance up to 90 MOPS

# TMS320C4x DMA Coprocessor Block Diagram

# **TMS320C4x Generation Summary**

This table gives a 'C4x-generation product summary so you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C4x Generation Summary Table**

|              |               |                       | Memory On-Chip |                |                    | Peripherals     |               |                    |                   |                                |

|--------------|---------------|-----------------------|----------------|----------------|--------------------|-----------------|---------------|--------------------|-------------------|--------------------------------|

| Data<br>Type | Device        | Cycle<br>Time<br>(ns) | RAM<br>(Words) | ROM<br>(Words) | Memory<br>Off-Chip | Parallel<br>Bus | Comm<br>Ports | DMA<br>Coprocessor | On-Chip<br>Timers | Package                        |

| point        | TMS320C40-50† | 40                    | 2K × 32        | Boot           | 4G × 32            | 2 ext.          | 6             | 6/12 channels      | 2                 | 325-pin PGA                    |

| 32-bit       | TMS320C40-60  | 33                    | 2K × 3⁄2       | Boot           | 4G × 32            | 2 ext.          | 6             | 6/12 channels      | 2                 | 325-pin PGA                    |

| word         | TMS320C44-50  | 40                    | 2K × 32        | Boot           | 32M × 32           | 2 ext.          | 4             | 6/12 channels      | 2                 | 304-pin<br>PQFP/388-pin<br>BGA |

|              | TMS320C44-60  | 33                    | 2K × 32        | Boot           | 32M × 32           | 2 ext.          | 4             | 6/12 channels      | 2                 | 304-pin<br>PQFP/388-pin<br>BGA |

<sup>†</sup>Military version available ‡Extended temperature version available

## TMS320C5x Generation

The 'C5x generation performs 20-50 million instructions per second (MIPS). The 3-V versions maintain 40 MIPS performance and reduce power consumption to 1.15 mA/MIPS. For more information on power consumption, TI provides the *Calculation of TMS3205x Power Dissipation Application Report* (SPRA030).

The 'C5x generation offers devices with a variety of memory mixes and peripheral options.

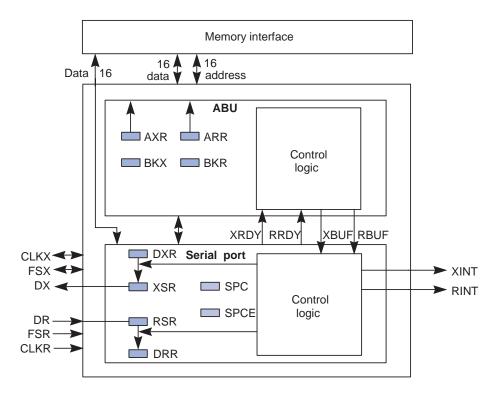

The standard synchronous, double-buffered serial port operates at up to 12.5 Mbps with independent transmit and receive sections. The time-division multiplexed (TDM) serial port has all of the same features as the standard serial port, yet TDM features make the serial port well suited for interprocessor communication in multiprocessor DSP systems. The buffered serial port (BSP) operates at up to 40 Mbps with no CPU intervention. The host port interface (HPI) is an 8-bit parallel port used to interface a host processor to the 'C5x.

Multiple on-chip phase-locked loop (PLL) options are available depending upon which 'C5x is used. The on-chip PLL allows lower frequency clocks, reducing power and electromagnetic emissions.

For systems requiring significant off-chip resources, the 'C5x family addresses 64K 16-bit words externally in program, data, and I/O spaces; each space has its own pin.

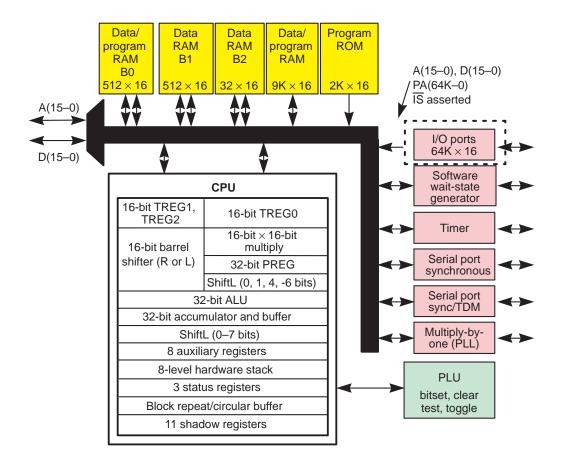

## **TMS320C5x**

The TMS320C5x accepts source code from the 'C1x, 'C2x, and 'C2xx generations. Faster cycle times, on-chip memories, a parallel logic unit (PLU), zero-overhead context switching, and block repeats differentiate the 'C5x. The integration of the IEEE 1149.1 (JTAG) test bus increases system reliability, allowing 99% fault grade testing and on-chip emulation. There is also an ANSI C compiler designed for the 'C5x, which translates the widely used ANSI C language directly into highly optimized assembly language for the 'C5x.

## TMS320C5x Enhancements

- 20-, 25-, 35-, and 50-ns instruction cycle times

- Zero-overhead context switching

- Parallel logic unit (PLU) for fast bit manipulation

- Up to 32K words on-chip memory

- IEEE 1149.1-standard (JTAG) scan-path test bus for system test and emulation

- Zero-overhead block repeats

- Delayed branch, call, and return instructions

- Two indirectly addressed circular buffers

- Software wait-state generation

- Various phase-locked loop (PLL) options for reduced EMI and system power dissipation

### TMS320C50

The TMS320C50 is a highly integrated DSP, offering a complete system on a single chip. With a boot ROM and 10K 16-bit words of on-chip RAM, an entire DSP system can be integrated into the 132-pin QFP package. By integrating the memory on chip, you reduce both power and board space. Integrating the off-chip memory can be especially important in high-performance systems to eliminate expensive high-speed SRAM.

#### Features of the 'C50 include:

- 25-, 35-, and 50-ns instruction cycle times

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Standard boot loader

- Full-duplex synchronous serial port

- Time-division multiplexed (TDM) serial port

- 132-pin BQFP package

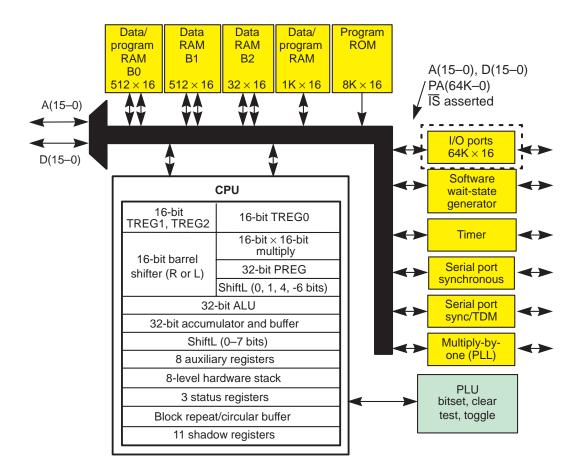

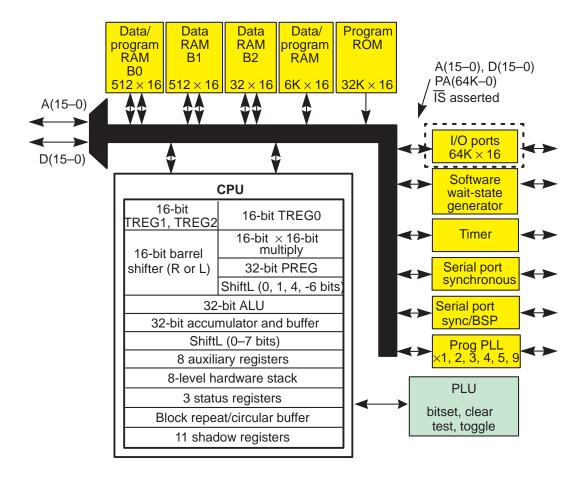

## TMS320C50 Block Diagram

### TMS320C51

In the TMS320C51, the 'C50's 9K-word block of RAM is replaced by 8K 16-bit words of on-chip ROM. This provides a considerable advantage in cost and performance for those who require large amounts of on-chip program space. With this ROM and 2K 16-bit words of RAM, sophisticated DSP algorithms can fit on a single device. This device is available in a 132-pin BQFP and a 100-pin TQFP that measures only  $14 \times 14 \times 1.4$  mm, for designs that require both small board area and reduced height.

#### Features included on the 'C51 are:

- 20-, 25-, 35-, and 50-ns instruction cycle times

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex synchronous serial port

- TDM serial port

- 132-pin BQFP and 100-pin TQFP packages

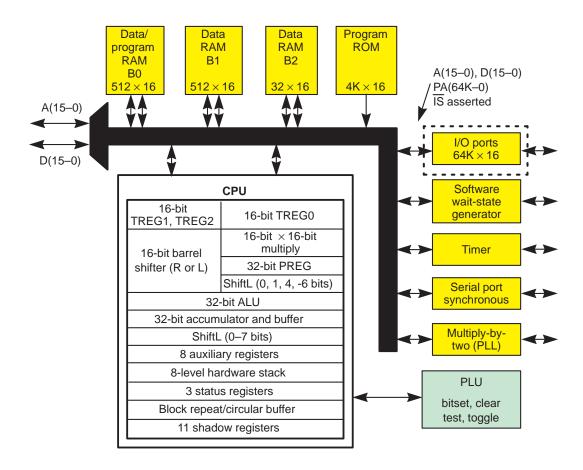

# TMS320C51 Block Diagram

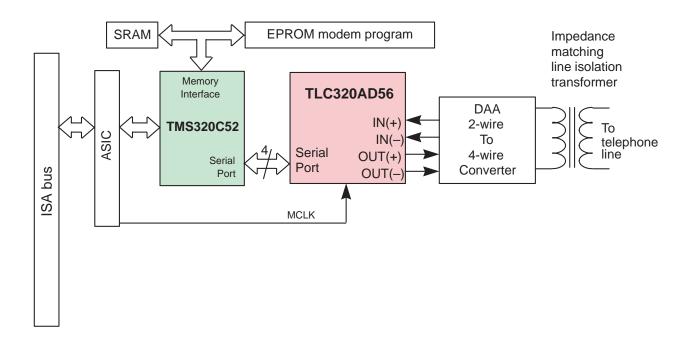

### TMS320C52

The TMS320C52 has a superb combination of both low cost and high performance. Traditionally, devices in the same price range have offered 10 MIPS performance. The 'C52 provides twice the performance (20 MIPS) and room to grow into a 50-MIPS version. The 4K 16-bit words of ROM can be configured with your code or purchased preprogrammed with a boot loader.

#### Additional features of the 'C52 include:

- 20-, 25-, 35-, 40-ns, and 50-ns instruction cycle times at 5V

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex synchronous serial port

- 100-pin BQFP and TQFP packages

- 3.31-V version

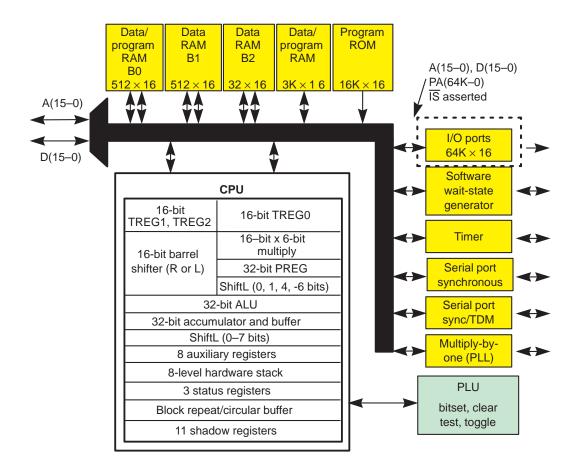

# TMS320C52 Block Diagram

### TMS320C53

The TMS320C53 provides greater integration of on-chip ROM than the 'C51. With 16K 16-bit words of on-chip ROM and 4K 16-bit words of on-chip RAM, an entire DSP system can be integrated into the 132-pin BQFP package. By bringing the memory on-chip, TI reduces both power and board space; on-chip memory also provides a considerable advantage in cost and performance.

#### The 'C53 features:

- 25-, 35-, and 50-ns instruction cycle times at 5V

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex synchronous serial port

- TDM serial port

- 132-pin BQFP package

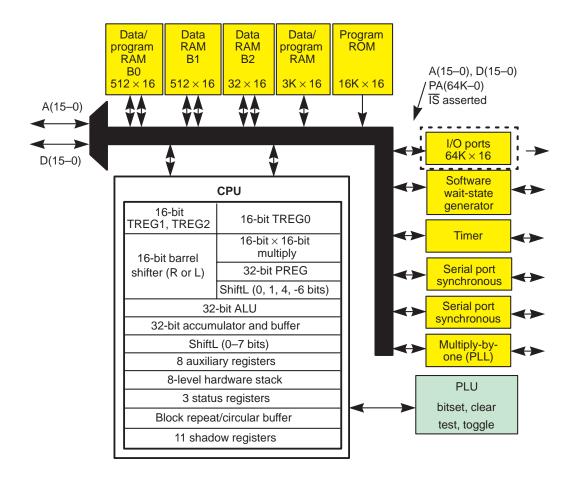

## TMS320C53 Block Diagram

### TMS320C53S

There are slight differences between the 'C53 and the 'C53S. In order to accommodate the integration capabilities of the 'C53 into a 100-pin TQFP package, some features were removed from the standard 'C53. The 'C53S offers two standard serial ports instead of the TDM and standard serial ports in the 'C53. The 'C53S has reduced capability of the on-chip analysis block and has no boundary scan.

#### Features included on the 'C53S are:

- 25-, 35-, and 50-ns instruction cycle times at 5V

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex synchronous serial port

- 100-pin TQFP package

- 40-ns (TMSLC320C53S) 3.3-V version

# TMS320C53S Block Diagram

### **TMS320LC56**

The TMS320LC56 provides greater integration of on-chip ROM than the 'C53. With 32K 16-bit words of on-chip ROM and 7K 16-bit words of on-chip RAM, the 'LC56 can accommodate large program and data spaces on-chip, minimizing off-chip accesses. The 'LC56 also provides a very fast buffered serial port (BSP) capable of 40 Mbps at 25-ns instruction cycle time. The 'LC56 is optimized for high-performance, low-power applications; as a result, it operates at 3.3 V only.

### Key features of the 'LC56 are:

- 25-, 35-, and 50-ns instruction cycle times at 3.3 V

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Programmable PLL

- Full-duplex synchronous serial port

- · Buffered serial port with dedicated bus

- 100-pin TQFP package

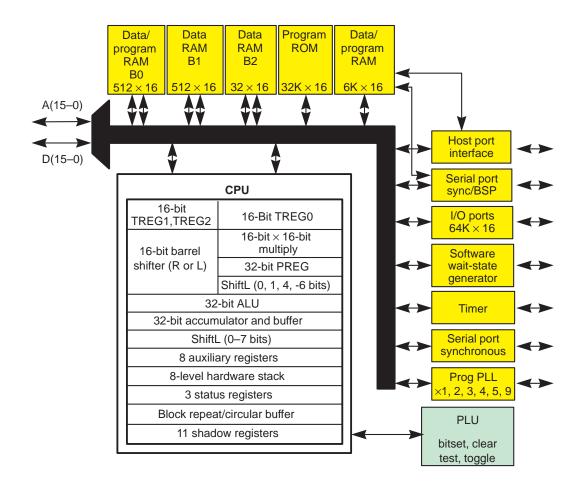

# TMS320LC56 Block Diagram

### TMS320LC57

The TMS320C57 incorporates the same amount of on-chip memory as the 'LC56 and offers a high-throughput buffered serial port (BSP). In addition, the 'LC57 provides an 8-bit wide host port interface (HPI) which can be used to communicate with other 'LC57 devices or embedded microprocessors. The 'LC57, like the 'LC56, is capable of a 25-ns instruction cycle time at 3.3 V.

#### The 'LC57 features:

- 25-, 35-, and 50-ns instruction cycle times at 3.3 V

- Boot load through HPI or standard serial port

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Boot ROM option

- Full-duplex synchronous serial port

- Programmable PLL

- Buffered serial port with dedicated bus

- Host port interface with dedicated bus

- 128-pin TQFP package

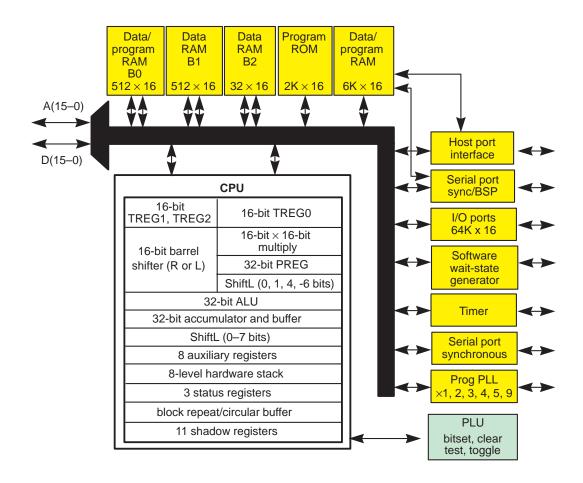

# TMS320LC57 Block Diagram

### TMS320C57S

The TMS320C57S takes advantage of the same peripherals that are on the 'LC57 to make the 'C57S a cost-effective embedded data I/O engine. In order to provide a broad-based appeal, the 'C57S differs from the 'LC57 in four ways:

- The 32K 16-bit words of ROM space has been replaced with a boot ROM

- The 'BC57S can operate at 5V

- The 144-pin package of the 'BC57S has a wider lead pitch than the package of the 'LC57

- The 'BC57S is lower in cost

#### Features of the 'C57S include:

- 25-, 35-, and 50-ns cycle times at 5V

- Standard boot loader

- 7K-word RAM

- Boot load through HPI or standard serial port

- 192K-word external address reach

- Accepts source code from the 'C1x/'C2x/'C2xx generations

- ANSI C compiler

- IEEE 1149.1-standard (JTAG) emulator control

- Full-duplex synchronous serial port

- Buffered serial port with dedicated bus

- Host port interface with dedicated bus

- 144-pin TQFP package

# TMS320C57S Block Diagram

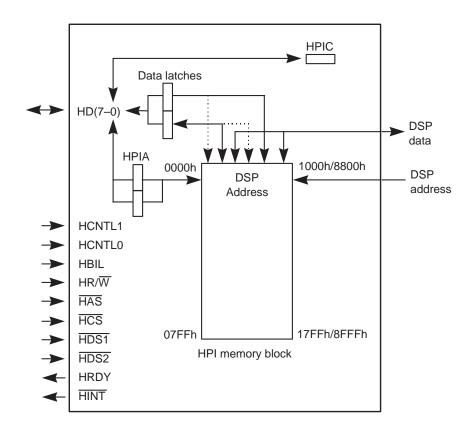

### TMS320LC57/'C57S Host Port Interface

The host port interface (HPI) is an 8-bit parallel port available on the TMS320LC57 and the TMS320C57S. The HPI provides a glueless interface to standard microprocessors as well as to other TI devices. The HPI appears as a 2K-word block of shared memory that is available in either a FIFO or standard random-access configuration. Most importantly, the HPI has the ability to maintain its high level of functionality as the interface between an external CPU and the 'C57, even while the 'C57 is idle or in reset. This significantly reduces system power consumption by offloading standard I/O tasks from the DSP.

#### Features of the HPI include:

- Byte-wide register addressability

- 8-bit parallel port

- High-speed back-to-back accesses

- Dedicated bus to a 2K 16-bit words of SARAM

- Shared-access mode (SAM)

- Normal mode of operation

- Allows DSP and host to have HPI memory access

- Asynchronous host accesses are resynchronized internally

- 45.7 Mbps at 57 MHz

- 64.0 Mbps at 80 MHz

- Host-only mode (HOM)

- Allows host to access HPI memory while 'C57 is in IDLE2 or in reset mode

- 5 μA power dissipation (IDLE2)

- 160 Mbps, independent of clock

# TMS320LC57/'C57S Host Port Interface Block Diagram

## TMS320LC56/'LC57/'C57S Buffered Serial Port

The buffered serial port (BSP) provides a no-overhead mechanism to interface serially with CODECs, ADCs, and other peripherals. The BSP supports 8-, 10-, 12-, and 16-bit serial data packets and uses a 2K-byte buffer to hold input or output data. Downward code compatible with the standard serial ports, the BSP is designed to be completely flexible and programmable. The BSP has the ability to simultaneously receive data from and transmit data to a programmable on-chip buffer via a dedicated memory bus, freeing the CPU to execute other tasks without memory bus contention.

# TMS320LC56/'LC57/'C57S BSP Block Diagram

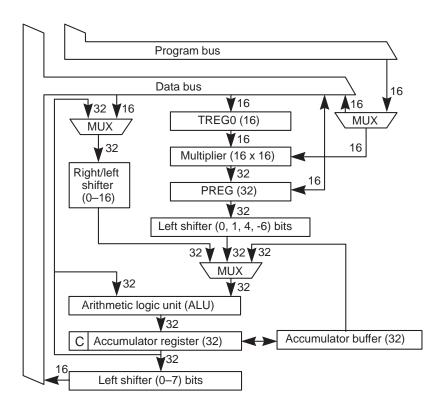

## TMS320C5x Multiplier/ALU Features

The performance and parallelism of the 'C5x architecture become evident by studying the multiplier and accumulator sections of the device. The on-chip multiplier performs a 16-bit  $\times$  16-bit multiply with a 32-bit product in a single cycle.

To double the performance, the 'C5x devices can fetch two data operands when executing the multiply and accumulate (MAC) instruction.

Scaling and fractional math shifts occur in parallel with all arithmetic operations.

The 'C5x devices are the first to include an accumulator buffer. The accumulator buffer provides quick comparisons to the accumulator contents to determine the minimum or maximum in a table of values, a common operation for both general-purpose and DSP algorithms. This is very useful in implementing Viterbi-decoding algorithms. Additionally, the accumulator buffer allows quick temporary storage of a commonly referenced value, which eliminates the extra cycles it takes to store the value in memory. It also allows up to 65 bit shifts among accumulator, accumulator buffer, and carry.

Features of the 'CC5x multiplier/ALU include:

- Single-cycle 16-bit × 16-bit multiply, yielding a 32-bit product

- Can access program and two data operands simultaneously

- CPU performs simultaneous ALU and multiplier operations

- Zero-overhead shift registers

- Accumulator buffer with path back into ALU

# TMS320C5x Multiplier/ALU Features Block Diagram

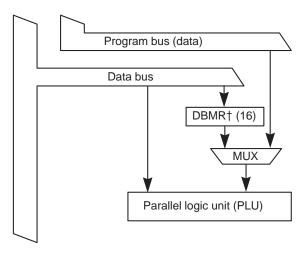

## TMS320C5x Parallel Logic Unit

The parallel logic unit (PLU) performs logical operations without corrupting the ALU contents. This allows data to be checked and decisions made without the overhead of storing and restoring the ALU content.

The PLU supports AND, OR, XOR, and compare functions. These functions are commonly used to set, clear, and toggle bits within a data-memory location. To make these functions easy to use, dedicated instructions perform them, using either immediate or register data to compare with the data-memory location.

#### Features of the 'C5x PLU are:

- Performs logical operations without disturbing arithmetic registers in ALU

- Sets, clears, and toggles any number or combinations of bits in data memory

- Compares bits individually or collectively

- Supports long immediate and register values

# TMS320C5x Parallel Logic Unit Block Diagram

#### **PLU Instructions**

| Mnemonic | Description                            |  |  |

|----------|----------------------------------------|--|--|

| APL#     | AND DBMR†/constant with data memory    |  |  |

| CPL#     | Compare DBMR/constant with data memory |  |  |

| OPL#     | OR DBMR/constant with data memory      |  |  |

| XPL#     | XOR DBMR/constant with data memory     |  |  |

| SPLK#    | Store long immediate to data memory    |  |  |

†DBMR: Dynamic bit-manipulation register

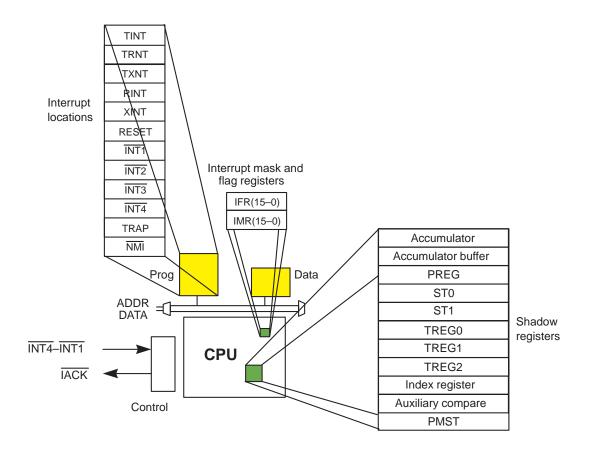

## TMS320C5x Interrupts

The TMS320C5x supports four external interrupts, two serial port interrupts, one timer interrupt, and a trap instruction.

To speed up interrupt service routines (ISR), the key registers are shadowed with a 1-level deep stack and are saved in a single cycle. This saves 22 cycles when an interrupt occurs by eliminating the need to push and pop these 11 registers.

The 'C5x interrupt features include:

- Interrupt sources: four external, two serial ports, one timer, one trap instruction

- 1-level deep stack on strategic registers for zero-overhead context switching

- Program-accessible interrupt flag register for software interrupt polling

- Automatic global interrupt enable on return from interrupt service routine

- Interrupt vectors are relocatable

# TMS320C5x Interrupts Block Diagram

## TMS320C5x Circular Addressing

Circular addressing is a method to address *aging* data sets for common DSP algorithms. For example, after performing the first set of calculations on an FIR filter data set, a new data value must be brought in and the oldest value discarded. DMOV allows you to do this by treating data in a circular fashion, with the oldest and newest values located side by side. At the end of each calculation, a new data value is placed in memory at the location of the oldest value. You update the circular buffer start address to correspond to the newest value and the circular buffer end address to correspond to the oldest value.

#### Circular addressing features:

- Two circular addressing data buffers

- Auxiliary registers are memory-mapped to indirectly address each circular buffer

- Effective use of data-memory space while increasing performance

# TMS320C5x Circular Addressing Block Diagram

Circular buffer control register

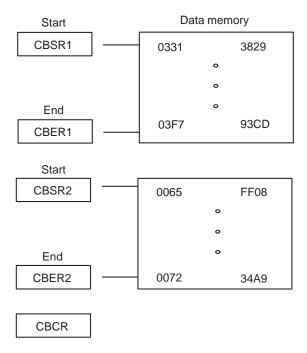

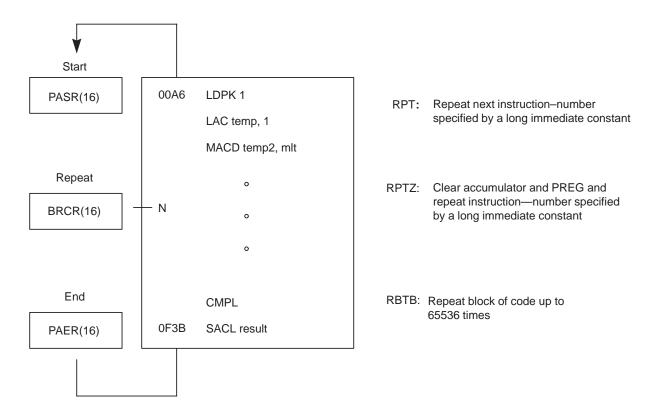

# **Repeat and Block Instructions**

The TMS320C25 was the first device to offer a zero-overhead looping instruction, the RPT instruction. The 'C5x expands this capability with the RPTZ and RPTB instructions. The RPTZ command is a logical extension of the RPT command that also clears the accumulator and product registers. This saves two cycles in typical routines. The repeat block instruction (RPTB) allows you to repeat a block of code up to 64K times without any overhead required to branch to the beginning of the code segment. This allows you to benefit from a faster instruction cycle (due to the pipeline) without paying a penalty for program discontinuity.

# **Repeat and Block Instructions Block Diagram**

# **TMS320C5x Generation Summary**

All TMS320C5x devices share the same CPU architecture and accept source code from all 'C1x, 'C2x, and 'C2xx devices.

This table gives a 'C5x-generation product summary so that you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C5x Generation Summary Table**

|             |                 |                |                           |                           |                              | Peripherals       |     |        |                              |

|-------------|-----------------|----------------|---------------------------|---------------------------|------------------------------|-------------------|-----|--------|------------------------------|

| Device      | Cycle Time (ns) | Voltage<br>(V) | On-Chip<br>ROM<br>(Words) | On-Chip<br>RAM<br>(Words) | External<br>Address<br>Range | Serial<br>Port(s) | HPI | Timers | Package                      |

| TMS320C50†  | 25/35/50        | 5.0V           | 2K                        | 10K                       | 192K                         | 2‡                | _   | 1      | 132-pin BQFP                 |

| TMS320LC50  | 25/40/50        | 3.3V           | 2K                        | 10K                       | 192K                         | 2‡                | _   | 1      | 132-pin BQFP                 |

| TMS320C51   | 20/25/35/50     | 5.0V           | 8K                        | 2K                        | 192K                         | 2‡                |     | 1      | 100-pin TQFP<br>132-pin BQFP |

| TMS320LC51  | 25/40/50        | 3.3V           | 8K                        | 2K                        | 192K                         | 2‡                | -   | 1      | 100-pin TQFP<br>132-pin BQFP |

| TMS320C52   | 20/25/35/50     | 5.0V           | 4K                        | 1K                        | 192K                         | 1§                | -   | 1      | 100-pin TQFP<br>100-pin TQFP |

| TMS320LC52  | 25/40/50        | 3.3V           | 4K                        | 1K                        | 192K                         | 1§                | -   | 1      | 100-pin TQFP<br>100-pin TQFP |

| TMS320C53   | 25/35/50        | 5.0V           | 16K                       | 4K                        | 192K                         | 2‡                | _   | 1      | 132-pin BQFP                 |

| TMS320LC53  | 25/40/50        | 3.3V           | 16K                       | 4K                        | 192K                         | 2‡                | _   | 1      | 132-pin BQFP                 |

| TMS320C53S  | 25/35/50        | 5.0V           | 16K                       | 4K                        | 192K                         | 2‡                | _   | 1      | 100-pin TQFP                 |

| TMS320LC53S | 25/40/50        | 3.3V           | 16K                       | 4K                        | 192K                         | 2§                | _   | 1      | 100-pin TQFP                 |

| TMS320LC56  | 25/35/50        | 3.3V           | 32K                       | 7K                        | 192K                         | <b>2</b> ¶        | _   | 1      | 100-pin TQFP                 |

| TMS320LC57  | 25/35/50        | 3.3V           | 32K                       | 7K                        | 192K                         | 2¶                | 1   | 1      | 128-pin TQFP                 |

| TMS320C57S  | 25/35/50        | 5.0V           | Boot                      | 7K                        | 192K                         | <b>2</b> ¶        | 1   | 1      | 144-pin TQFP                 |

| TMS320LC57S | 35/50           | 3.3V           | Boot                      | 7K                        | 192K                         | 2¶                | 1   | 1      | 144-pin TQFP                 |

<sup>†</sup> Military version available ‡=Standard serial port and TDM serial port §=Standard serial port ¶=Standard serial port and 1 buffered serial port

### TMS320C54x Generation

The TMS320C54x generation of DSPs integrate functions to improve performance, lower chip count, and reduce power consumption to enable greater system cost savings. The devices combine high-performance, a large degree of parallelism, and a specialized instruction set to effectively implement a variety of complex algorithms and applications.

Features include a Viterbi accelerator, four internal buses, dual-address generators, 40-bit adder, two 40-bit ALUs, eight auxiliary registers, and a software stack.

### TMS320C54x Enables High Performance, Emerging Applications

The 'C54x architectural efficiencies — high MIPS and low power dissipation — make it an ideal device for a variety of wireless and wireline communications systems. Standard wireless applications like cellular handsets can take advantage of the 'C54x's power-down modes, high performance, and large ROM memory spaces for integrating entire algorithms on chip. The high performance and large RAM are useful for reconfigurable systems where a variety of different algorithms must be executed from on-chip memory. Data communications or telephony applications can increase the functionality of their systems while lowering systems costs by allowing the 'C54x to absorb the existing system functionality of multiple-DSP implementations.

# TMS320C54x Enables High Performance, Emerging Applications

- Digital cellular basestations

- Personal communications systems (PCS)

- V.34/ISDN modems

- Mobile radios

- Personal digital assistants (PDAs)

- Networking

- T1/E1 or PBX trunks

- Wireless data (CDPD)

- Wireless handsets (TDMA or CDMA standards)

- Digital Cordless (DECT, CT2, PHS)

- Pagers

- Satellite modems

- Voice-over internet protocol

- Multifunction telephony line cards in LAN

- Wireless local loop

- Multimedia/telephony integration (fax/data + 3-D sound, etc.)

- Cable modems

- Set-top boxes

### TMS320C54x CPU Key Features

The TMS320C54x and TMS320LC54x fixed-point digital signal processors are fabricated with an advanced modified Harvard architecture that has one program memory bus, three data memory buses, and four address buses. The core's key features include a 17-bit  $\times$  17-bit multiplier (16-bit signed or unsigned), a dedicated 40-bit adder for nonpipelined MAC (multiply/accumulate) operation, a separate 40-bit ALU for increased parallelism, two 40-bit accumulators, and a compare, select, store unit (Viterbi accelerator). The 'C54x utilizes a highly specialized dual-operand instruction set, which is the basis of the operational flexibility and speed of these DSPs. The 'C54x also includes eight auxiliary registers and a software stack to enable a highly-optimized C compiler. The device's lower power consumption and reduced chip count, and enable system cost savings for communications applications.

### TMS320C54x CPU Key Features

- Advanced multibus architecture with three separate 16-bit data buses and one program bus, three data buses, and four address buses

- 40-bit arithmetic logic unit (ALU), including a 40-bit barrel shifter and two independent 40-bit accumulators

- 17-bit × 17-bit parallel multiplier coupled to a 40-bit dedicated adder for nonpipelined, single-cycle multiply/accumulate (MAC) operation

- Compare, select, store unit (CSSU) for the add/compare selection of the Viterbi operator

- Exponent encoder to compute the exponent of a 40-bit accumulator value in a single cycle

- Two address generators, including eight auxiliary registers and two auxiliary register arithmetic units (ARAUs)

### TMS320LC541

#### Features of the 'LC541 include:

- 25-ns (40 MIPS) or 20-ns (50 MIPS) instruction cycle time ('C541 available only at 25 ns)

- Various operating voltages

- 3.3 V ('LC541)

- 5.0 V ('C541)

- 28K 16-bit words of ROM and 5K 16-bit words of RAM on chip

- Integrated Viterbi accelerator

- Powerful single-cycle instructions (dual-operand, parallel, and conditional instructions)

- Low active-mode power dissipation

- Less than 35 mW to run VSELP

- Low-power standby modes

- 100-pin TQFP package

- Multiple PLL options

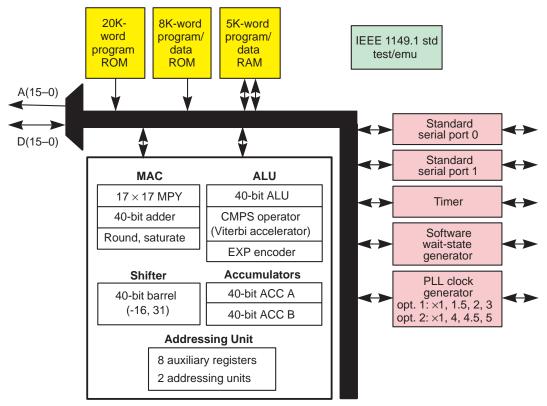

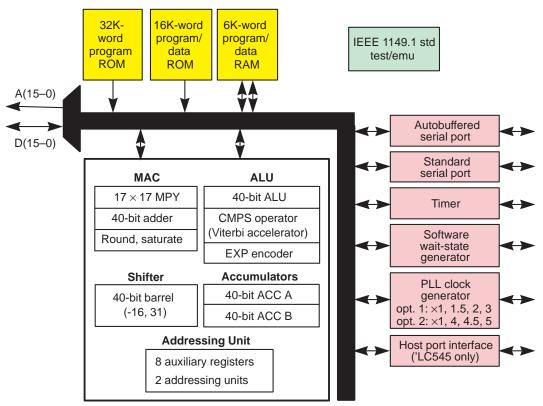

# TMS320LC541 Block Diagram

Note: The 'LC541 is available with one of two different PLL options. You choose one of the options listed.

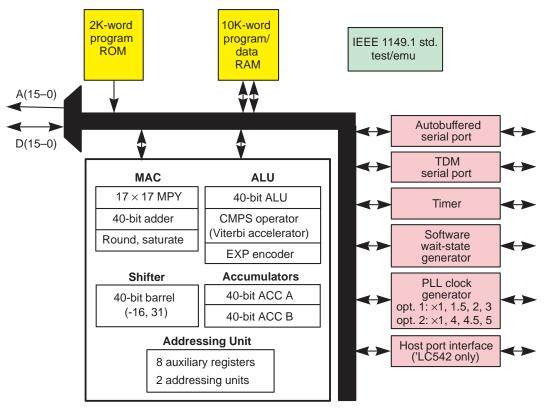

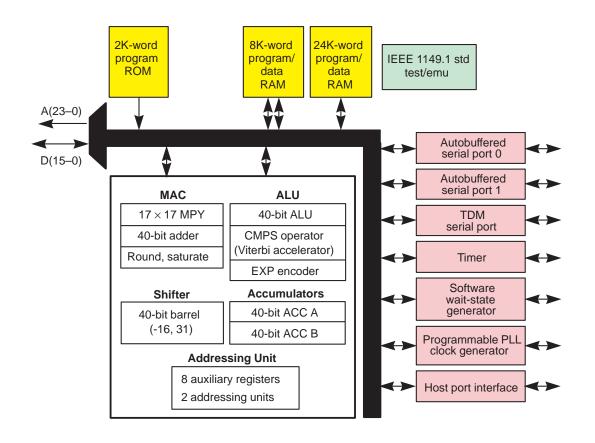

### TMS320LC542 and TMS320LC543

#### The 'LC542 and 'LC543 feature:

- 25-ns (40 MIPS) or 20-ns (50 MIPS) instruction cycle time ('C542 available only at 25 ns)

- Various operating voltages

- 3.3 V ('LC542, 'LC543)

- 5.0 V ('C542)

- 10K 16-bit words of RAM and 2K 16-bit words of on-chip boot ROM

- Autobuffered serial port (BSP)

- Time-division multiplexed serial port (TDM)

- Host port interface (HPI)

- Integrated Viterbi accelerator

- Powerful single-cycle instructions (dual-operand, parallel, and conditional instructions)

- Low active-mode power dissipation

- Less than 35 mW to run VSELP

- Low-power standby modes

- 'LC542: 128- and 144-pin TQFP packages

- 'LC543: 100-pin TQFP package (without HPI)

### TMS320LC542 and TMS320LC543

Note: The 'LC542 and 'LC543 are available with one of two different PLL options. You choose one of the options listed.

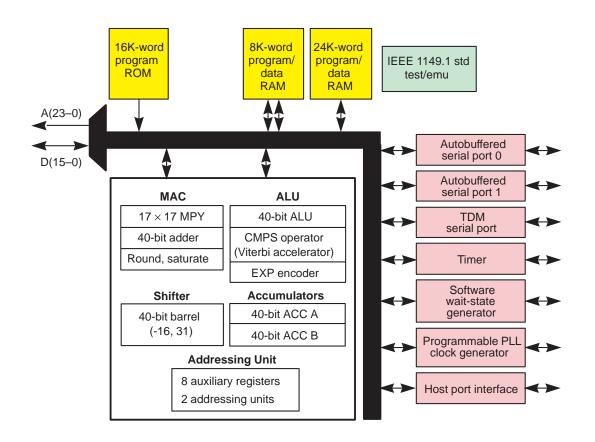

### TMS320LC545 and TMS320LC546

#### The 'LC545 and 'LC546 feature:

- 25-ns (40 MIPS) or 20-ns (50 MIPS) instruction cycle time

- Various operating voltages

- 3.3 V ('LC545, 'LC546)

- 48K 16-bit words of ROM and 6K 16-bit words of RAM on chip

- Autobuffered serial port (BSP)

- Host port interface (HPI)

- Integrated Viterbi accelerator

- Powerful single-cycle instructions (dual operand, parallel instructions, conditional instructions)

- Low active-mode power dissipation

- Less than 35 mW to run VSELP

- Low-power standby modes

- 'LC545: 128-pin TQFP package

- 'LC546: 100-pin TQFP package (without HPI)

### TMS320LC545 and TMS320LC546

Note: The 'LC545 and 'LC546 are available with one of two different PLL options. You choose one of the options listed.

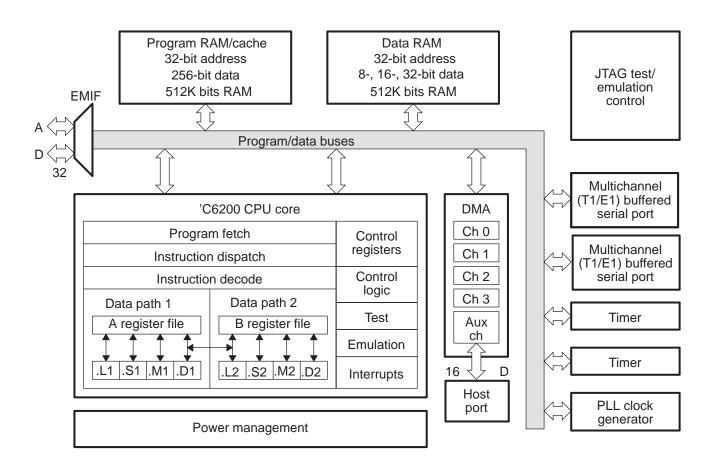

### TMS320LC548

#### The 'LC548 features:

- 12.5-ns (80 MIPS) or 15-ns (66 MIPS) instruction cycle times

- 3.3-V operation

- 32K 16-bit words of RAM and 2K 16-bit words of boot ROM on-chip

- Extended addressing mode for 8M × 16-bit maximum addressable external program space

- Two autobuffered serial ports (BSPs)

- TDM serial port (HPI)

- Host port interface

- Integrated Viterbi accelerator

- Powerful single-cycle instructions (dual operand, parallel instructions, conditional instructions)

- Low active-mode power dissipation

- Less than 35 mW to run VSELP

- Low-power standby modes

- JTAG with boundary scan

- 16-bit on-chip timer

### TMS320LC548

### TMS320LC549/'VC549

#### The 'LC549 and 'VC549 features:

- 10-ns (100 MIPS), 12.5-ns (80 MIPS), or 15-ns (66 MIPS) instruction cycle times

- 'VC549

- 2.5V core and 3.3V input/output

- 'LC549

- 3.3V operation

- 32K 16-bit words of RAM and 16K 16-bit words of boot ROM on-chip

- Extended addressing mode for 4M x 16-bit maximum addressable external program space

- Two autobuffered serial ports (BSPs)

- TDM serial port

- Host port interface (HPI)

- Integrated Viterbi accelerator

- Powerful single-cycle instructions (dual operand, parallel instructions, conditional instructions)

- Low active-mode power dissipation

- Less than 35 mW to run VSELP

- Low-power standby modes

- JTAG with boundary scan

- 16-bit on-chip timer

### TMS320LC549/'VC549

# **TMS320C54x Generation Summary**

All TMS320C54x devices share the same CPU architecture. This table gives a 'C54x-generation product summary so that you can choose the best combination of performance, memory, power, package, and peripherals for your system.

# **TMS320C54x Generation Summary Table**

|             |                                   |                    | On-Chip Memory Peripherals |                |                   |     |        |                              |

|-------------|-----------------------------------|--------------------|----------------------------|----------------|-------------------|-----|--------|------------------------------|

| Device      | Nominal<br>Voltage (V)<br>(± 10%) | Cycle<br>Time (ns) | RAM<br>(Words)             | ROM<br>(Words) | Serial<br>Port(s) | НРІ | Timers | Package                      |

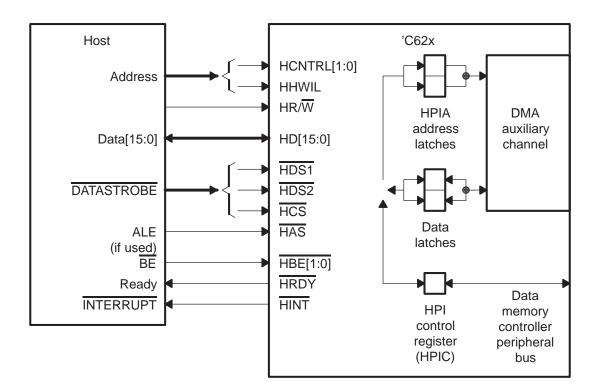

| TMS320C541  | 5.0                               | 25                 | 5K                         | 28K            | 2                 | No  | 1      | 100-pin TQFP                 |